# Ferroelectric materials for neuromorphic

Cite as: APL Mater. 7, 091109 (2019); https://doi.org/10.1063/1.5108562 Submitted: 30 April 2019 . Accepted: 05 September 2019 . Published Online: 19 September 2019

S. Oh (10), H. Hwang (10), and I. K. Yoo (10)

## **COLLECTIONS**

Paper published as part of the special topic on Emerging Materials in Neuromorphic Computing Note: This paper is part of the Special Topic on Emerging Materials in Neuromorphic Computing.

FP This paper was selected as an Editor's Pick

## ARTICLES YOU MAY BE INTERESTED IN

Ferroelectricity in hafnium oxide thin films

Applied Physics Letters 99, 102903 (2011); https://doi.org/10.1063/1.3634052

Perspective: A review on memristive hardware for neuromorphic computation Journal of Applied Physics 124, 151903 (2018); https://doi.org/10.1063/1.5037835

A critical review of recent progress on negative capacitance field-effect transistors Applied Physics Letters 114, 090401 (2019); https://doi.org/10.1063/1.5092684

# Ferroelectric materials for neuromorphic

Cite as: APL Mater. 7, 091109 (2019); doi: 10.1063/1.5108562 Submitted: 30 April 2019 • Accepted: 5 September 2019 • **Published Online: 19 September 2019**

S. Oh, D H. Hwang, D and I. K. Yoo D

## **AFFILIATIONS**

Center for Single Atom-based Semiconductor Device and Department of Material Science and Engineering, Pohang University of Science and Technology, Pohang 37673, South Korea

Note: This paper is part of the Special Topic on Emerging Materials in Neuromorphic Computing. a) Author to whom correspondence should be addressed: inyoo@postech.ac.kr

### **ABSTRACT**

Ferroelectric materials are promising candidates for synaptic weight elements in neural network hardware because of their nonvolatile multilevel memory effect. This feature is crucial for their use in mobile applications such as inference when vector matrix multiplication is performed during portable artificial intelligence service. In addition, the adaptive learning effect in ferroelectric polarization has gained considerable research attention for reducing the CMOS circuit overhead of an integrator and amplifier with an activation function. In spite of their potential for a weight and a neuron, material issues have been pointed out for commercialization in conjunction with CMOS processing and device structures. Herein, we review ferroelectric synaptic weights and neurons from the viewpoint of materials in relation to device operation, along with discussions and suggestions for improvement. Moreover, we discuss the reliability of HfO2 as an emerging material and suggest methods to overcome the scaling issue of ferroelectrics.

© 2019 Author(s). All article content, except where otherwise noted, is licensed under a Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/). https://doi.org/10.1063/1.5108562

# INTRODUCTION

The use of ferroelectric thin films was recommended for the connection of elements according to the need of the development of integrated circuit devices that directly facilitate the use of artificial neural network (ANN) as analog circuits in 1989. The ferroelectric synaptic weight for a neural network was demonstrated by a single bit memory effect or a multilevel memory effect in the form of a ferroelectric capacitor, 1,2 ferroelectric field effect transistor (FeFET), and ferroelectric tunnel junction (FTJ). 11-13 Moreover, the ferroelectric weight was reported to be controlled by spiketiming-dependent plasticity (STDP). 14-17 The ferroelectric neuron, which generates a pulse that activates a new input, was demonstrated on the basis of an adaptive learning function. 18-21 Neurons (preand post-) connecting via a three-terminal FeFET made of a ferroelectric thin-film transistor (TFT) was studied.<sup>22</sup> A ferroelectric neuron consisting of a ferroelectric capacitor on FinFET was also demonstrated.<sup>23</sup> In addition to ceramic ferroelectrics, organic ferroelectric weights were also investigated.<sup>24–26</sup> Even the ferroelectric

liquid crystal was studied for the optical neural network in  $1989.^{2}$

Ferroelectric weights are applied to both ANN and STDP with different operation. Typical wave forms to operate ferroelectric weight are well summarized in Ref. 16, where amplitude and pulse width modes are shown for ANN and prespike and postspike wave forms are shown for STDP.

The FeFET type is mainly used for STDP and various device types, for ANN. The taxonomy of ferroelectric synaptic weight for ANN, organized on the basis of the above reports, is listed in Table I. It is similar to that of ferroelectric memories because the memory can be directly applied to synaptic weight. The three-terminal structure, namely, a single Tr node for STDP, is well demonstrated in Refs. 5, 14-16 and 22. This article will mainly focus on ANN when it comes to ferroelectric weight.

In this article, we present several issues and limitations of ferroelectrics, mainly conventional ferroelectrics and HfO2-based ferroelectrics, and clarify how ferroelectrics can be used in neuromorphic applications such as synaptic weights and neurons.

**ARTICLE** APL Materials scitation.org/journal/apm

TABLE I. Taxonomy of ferroelectric synaptic weight for ANN.

| Weight cell struct | ures                 | Weight cell nodes                   | References                         |  |

|--------------------|----------------------|-------------------------------------|------------------------------------|--|

| Two-terminal       | 1R<br>1T-1R<br>1T-1C | FTJ<br>FTJ<br>Capacitor             | 13 and 17<br>11<br>1 and 6         |  |

| Three-terminal     | 1Tr                  | NOR<br>AND<br>Inverter<br>Single Tr | 28<br>29 and 30<br>31<br>32 and 33 |  |

## FERROELECTRIC SWITCHING

The size of ferroelectric capacitors should be carefully considered when studying synaptic weight and neuron of ferroelectrics

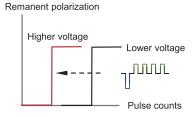

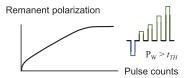

because ferroelectric switching behavior changes with decreasing ferroelectric size. Figure 1 describes the ferroelectric switching behavior depending on ferroelectric size and the input signal. Ishiwara investigated partial switching of PbZrTiOx (PZT) in detail and termed it adaptive learning.<sup>3</sup> Ferroelectric switching is caused by ferroelectric domain switching. Ishibashi and Takagi interpreted the switching transients of various ferroelectric crystals based on Kolmogorov's method. 34,35 They considered the domain nucleation rate and developed a model based on the time-dependent switching current. According to their model, a pulse width less than that of the full-domain switching time gives rise to partial domain switching. Ishiwara reported on polarization vs pulse width and pulse counts with a specific pulse width<sup>4</sup> through partial switching modeling.4,36

The polarization level based on partial switching in ferroelectrics is determined by both pulse width and voltage according to the following polarization equation: 4,14,37

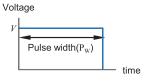

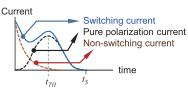

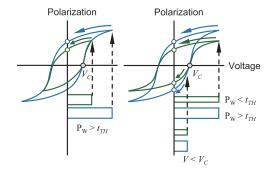

(a) Components of ferroelectric switching current.

(b) Effects of pulse width and pulse voltage on polarization reversal

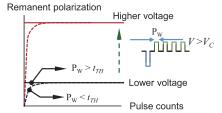

(c) Polarization under constant voltage pulses. Modeled based on Ref.[4]

(d) Polarization under constant voltage pulses for nanoscale ferroelectric capacitor of single domain. Modeled based on Ref.[38]

(e) Polarization under incremental voltage pulses. Modeled based on Ref.[32]

(f) Polarization under incremental voltage pulses for nanoscale ferroelectric capacitor consisting of multidomains with different coercive fields. Partially adapted from Ref.[39, 40]

$$P(t) = P_s \left\{ 1 - 2 \exp \left[ -\frac{t}{t_s} \exp \left( -\frac{E_a}{V/d_{FE}} \right)^n \right] \right\}, \tag{1}$$

where  $P_s$  represents spontaneous polarization,  $E_a$  is the activation electric field,  $d_{FE}$  is the ferroelectric film thickness, n is a constant used to describe the nucleation mechanism, and  $t_s$  is the switching time. Ishiwara observed partial polarization when applied pulse width was shorter than threshold switching time  $t_{TH}$ [Fig. 1(a)] where the maximum switching current was measured.<sup>4</sup> He applied a short pulse train to the PZT capacitor and obtained the curve of polarization and pulse count showing pulse-voltage dependency. Figure 1(c) shows the schematic curve of this relationship. To explain pulse-count dependence on partial switching, Ishiwara assumed that the pulse count is directly proportional to t in Eq. (1). Recently, Oh et al. and Kinder et al. demonstrated the multilevel states of HfO2 with respect to an incremental voltage mode and a pulse-width effect on polarization reversal in both HfZrOx (HZO) and PZT, respectively. 32,33 Equation (1) explains the incremental voltage dependency of polarization in Refs. 32 and 33 in conjunction with the schematic model shown in Fig. 1(e).

However, Eq. (1) is valid for relatively large sizes of a ferroelectric capacitor with many grains and domains. In the neuromorphic synapse application, highly scaled devices are required eventually. Therefore, a nano-sized FeFET will have limitation for use in multilevel states because it has either single grain or single domain in which multilevel switching is difficult. Therefore, different physics should be considered in a nanoscale ferroelectric capacitor. Mulaosmanovic *et al.* studied accumulative polarization reversal and single-domain switching in nanoscale FeFETs with a small number of ferroelectric grains. They applied a nucleation-dominated switching model to the nanoscale HfO<sub>2</sub> FeFET with a purely nucleation-limited model. Moreover, they studied switching time  $t_s$  in detail in conjunction with ferroelectric nucleation time  $\tau_0$  and time  $\Delta T_i$  between each critical nucleus generation,

$$t_{S} = \sum_{i=1}^{m} \Delta T_{i}, \tag{2}$$

where  $m \ge 1$ .<sup>40</sup> They assumed the nucleation to be the Poisson process and proposed the probability density function of  $\Delta T_i$  as

$$p_{\Delta T_i} = \lambda e^{-\lambda \Delta T_i},\tag{3}$$

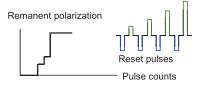

where  $\lambda$  is the nucleation generation rate. Furthermore, they observed electrical excitation in a FeFET, followed by a sudden and complete switching, as schematically shown in Fig. 1(d). As shown, binary switching ("off" and "on" switching) appears in fewer pulse counts with an increase in the pulse voltage in the nanoscale ferroelectric capacitor. Mulaosmanovic *et al.* also demonstrated multilevels in a nanoscale FeFET by controlling the program and erasing signals by applying incremental voltage pulses with reset pulses for every step, as schematically shown in Fig. 1(f). This implies that the use of multilevels is possible by using multidomains with different coercive voltages, even in a nanoscale ferroelectric device. <sup>39,40</sup>

The above-mentioned switching properties provide us with an integration guideline for ferroelectric weight. The multilevel weight of a certain sized ferroelectric capacitor can be realized by integrating 1T-1C and 1Tr cells. However, intermediate levels disappear in a nanoscale ferroelectric capacitor with binary weight. Therefore, a

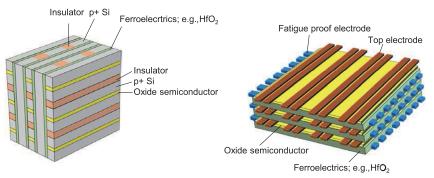

stacked structure, such as a cross-point structure, should be considered for developing multibit weights, as ferroelectrics are scaled down. A typical stacked cross-point structure for 1Tr node may be similar to the structure of a vertical NAND. The ferroelectric TFT is also another option for stack integration, in which an oxide semiconductor replaces Si. This is discussed in the emerging material section in more detail.

## FERROELECTRIC WEIGHT

Ferroelectrics have been considered for synaptic weights because of their nonvolatile multilevel memory properties.  $^{32}$  Although a floating gate transistor also exhibits a multilevel storage effect, its operating voltage is higher than that of a ferroelectric transistor. Moreover, a ferroelectric transistor exhibits endurance for more than  $10^9$  switching cycles when a fatigue free electrode or a buffer layer for a specific ferroelectric material is integrated as an electrode.  $^{41}$

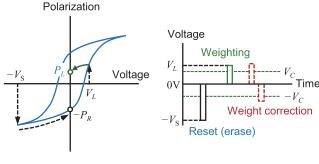

The multilevel polarization states of ferroelectrics can be achieved by applying either an incremental or constant voltage with a pulse width that results in partial polarization reversal <sup>1,3,4</sup> for a ferroelectric capacitor with a certain size and thickness. A ferroelectric capacitor has nonlinear multilevel polarization under both incremental voltage pulses and partial switching short pulses with a constant voltage. Furthermore, it is desirable for a ferroelectric capacitor to apply incremental and decremental pulses for multilevel synaptic weight in full range of polarization.

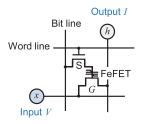

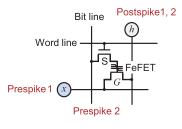

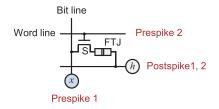

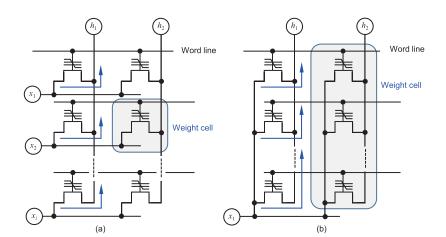

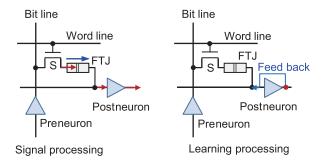

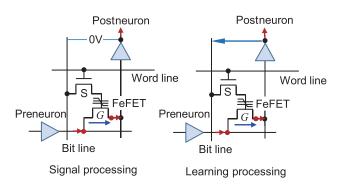

A ferroelectric synaptic weight comprises either three-terminal (1Tr) or two-terminal (FTJ) weight nodes. A very thin ferroelectric capacitor may create an FTJ that produces a binary polarization, in general. The FTJ cell forms a 1T-1R structure and comprises a twoterminal weight. Both 1Tr and 1T-1R nodes are operated in the conducting mode during weighting and multiplication. Figure 2 shows the operational scheme for both three- and two-terminal structures of a ferroelectric synaptic weight for ANN and STDP. For ANN, the weight is controlled by the gate that is independent of the input line in a three-terminal cell structure, whereas the weight is controlled by the input line in a two-terminal weight cell structure. The conductivity of the weight node increases (potentiation) and decreases (depression) based on pulse amplitude modulation or pulse width modulation. Furthermore, the relative timing between the prespike and postspike is converted to voltage height modulation across the synapse in STDP. 11,14,1

In a neural network, the input signal and weight are independently controlled. The input signal of the neural network typically comprises voltage pulses, and both input voltage and input pulse counts may vary depending on the input information. In addition, the weight is determined during learning and should be accessible randomly, directly, and independently. The dynamic range of the weight is determined by  $P_{\rm r}$  of ferroelectrics, i.e., positive and negative  $P_{\rm r}$ . The weight resolution and multilevel of polarization are controlled in this dynamic range, and this limits the weight bit-width in the ferroelectric synapse. Therefore, ferroelectrics with higher  $P_{\rm r}$  are desired. Nonlinear polarization against weighting (programming) voltage is also an issue. Thus, it is recommended that the information about weighting voltage and the corresponding polarization value should be stored separately to be used when weighting and unweighting. Figure 3 demonstrates how to control weight values

Bit line Word line Output I

Select transistor S controls ferroelectric transistor showing matrix multiplication [7]

Select transistor S controls ferroelectric tunnel junction showing matrix multiplication.

(a) Three terminal and two terminal synaptic weight in ANN

Select transistor S controls ferroelectric transistor showing STDP function[14].

Select transistor S controls ferroelectric tunnel junction showing STDP function[10].

(b) Three terminal and two terminal synaptic weight for STDP function

randomly and directly. Although a narrow pulse width with incremental pulse voltage may be considered for controlling multilevel polarization, nonlinearity would still be observed, and pulse count information should be stored.

## 1Tr for multilevel ferroelectric weight

1Tr-type multilevel weight is useful for vector matrix multiplication (VMM) in ANN. VMM in ANN can be classified as a

weight correction FIG. 3. Random and direct control of weight values. (a) Erasing process is neces-

(b) Pulse scheme for weighting and

sary before programming for direct weighting. The weighting voltage information should be stored for a specific weight value. (b) Precise weight control can be carried out by incremental pulses (or PWM) or reversely incremental pulses.

conductance- and capacitance-based multiplication. The relation I = GV corresponds to a typical conductance-based multiplication, where I is the output current, G is the conductance, and V is the input voltage. The capacitance-based multiplication adopts the relation Q = CV for a capacitive weight in a neural network, where Qis the output charge, C is the capacitance, and V is the input voltage. A ferroelectric gate transistor with a three-terminal structure is operated in the capacitive and conductive modes during weighting and matrix multiplication, respectively. This study mainly focused on conductance-based multiplication with respect to ferroelectric weight. Figure 4(a) shows a NOR-type ferroelectric weight in ANN that can perform VMM. The input lines are perpendicular to the output lines, and each cell conductance can be read by applying voltage pulses to the input lines simultaneously, by which output currents are measured simultaneously. Multilevel FeFETs can be recognized by reading channel conductance of each NOR cell. Therefore, a NOR structure with multilevel ferroelectric weight is an ideal hardware architecture for VMM.

FIG. 2. Cell structures and network con-

nections of conductance-based ferroelectric weights in 1Tr and 1T-1R types. (a) Weights in ANN and (b) those in

STDP.

## 1Tr for binary ferroelectric weight

The binary weight system is indispensable when a nanoscale ferroelectric device is integrated. However, binary weight may be applied even to a larger ferroelectric capacitor depending on an application such as the binary neural network. As ferroelectrics have a bistable state, bipolar voltage pulses at voltages higher than the coercive voltage are applied to achieve the binary weight. The positive and negative remanent polarizations (Pr) are designated as "1"

(a) Direct weighting

**FIG. 4.** NOR-type (a) and AND-type (b) ferroelectric synaptic weights. The NOR weight has nonlinear multilevel weights. In contrast, the AND weight with a group of single bits gives linear multibit weights.

and "0," respectively. Then, a single weight bit or binary weight per cell can be realized. A group of 1Tr binary-weight ferroelectric cells is required for achieving a multibit weight. A typical 1Tr group weight structure is similar to the AND-type ferroelectric weight, as shown in Fig. 4(b), <sup>3,29,31,42</sup> which originates from the AND-type ferroelectric storage. <sup>43</sup> Each FeFET represents a single-bit weight (binary weights "1" and "0"), and multilevels are recognized by reading as many as "on state" ferroelectric transistors.

The AND-type ferroelectric weight may guarantee a linear wide dynamic range of weights, but the wiring circuit becomes a critical issue in this case. The current level will also become limited to guarantee a practical dynamic range of weights. For example, when the weight bit is 16 bit and the current resolution is 1 nA, the system should be able to read from 1 nA through 66  $\mu$ A/weight cell. Then, the number of weight cells will be limited by available power even for the input voltage pulses. Therefore, the channel current of a ferroelectric transistor should be minimized for AND-type binary synaptic weights.

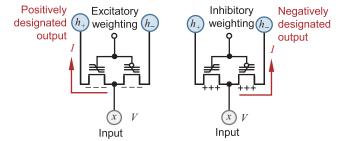

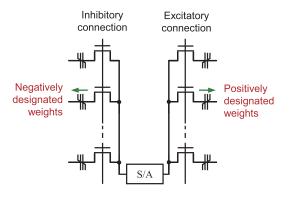

# 1Tr for ferroelectric bi-weight

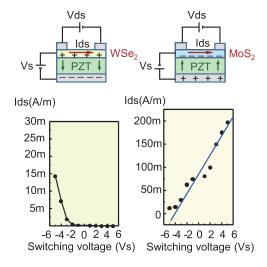

The most powerful property of FeFET is bistability, by which both excitatory and inhibitory weights can be achieved in a single cell. Figure 5 illustrates ferroelectric bi-weight cell operation, in which the cell structure consists of NMOS and PMOS. The weight cell with a ferroelectric inverter for both positive and negative weights was patented by Hynix. <sup>29</sup> Nishitani *et al.* fabricated PZT TFT by depositing an oxide semiconductor on PZT. <sup>15</sup> The biweight effect is enhanced when p-type and n-type materials are deposited on ferroelectrics. Figure 5(c) shows PZT TFT with transition metal dichacogenides deposited on it where p-type WSe<sub>2</sub> and n-type MoS<sub>2</sub> were used as channel materials. The ferroelectric TFT is useful for stacked ferroelectric weight.

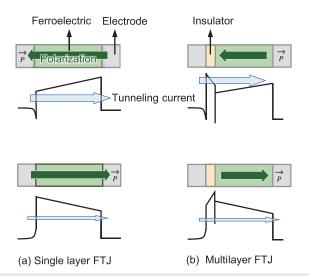

# 1T-1R or 1R for FTJ weight

Tsymbal and Kohlstedt reported about tunneling across a ferroelectric,<sup>44</sup> although the basic principle was reported by Esaki *et al.* in IBM.<sup>45</sup> Esaki *et al.* studied and formulated polar switch in 1971, following which Tsymbal and Kohlstedt established the FTJ concept.

(a) Positive ferroelectric weight (b) Negative ferroelectric weight

(c) Bi-weight of ferroelectric TFT for p-type and n-type transition metal dichlacogenide on PZT

**FIG. 5.** Biweight of ferroelectrics for ANN. Multilevel biweight in ferroelectric synaptic weight with a pair of (a) NMOS and (b) PMOS ferroelectric transistors. Positive output current and negative output current are designated by the current direction. (c) Ferroelectric TFT for biweight n-type and p-type weights is determined by semiconducting materials on ferroelectrics for TFT. Partially adapted from Patent KR 10-2018-0035251.

**FIG. 6.** FTJ model and weighting principle partially adapted from Ref. 46. (a) High and low tunneling currents are determined by the ferroelectric polarization direction. (b) Insulating film such as  $SiO_2$  or  $Al_2O_3$  can be integrated to protect the ferroelectric tunneling film.

FTJ is a nondestructive readout node as that of the resistive change memory. Figure 6 represents a simple description of the binary FTJ weight principle. A ferroelectric thin film should be thin enough to allow tunneling and thick enough to guarantee ferroelectric polarization switch. This contradictory requirement makes it difficult for FTJ to have multilevel weight. In addition, the polycrystalline ferroelectric thin film in FTJ induces high leakage current, and its practical device applications are thus difficult. Therefore, some insulating layer is integrated with FTJ to improve its performance. 46,47 The tunneling model of the multilayer FTJ is illustrated in Fig. 6(b).

Chanthbouala *et al.* suggested new applications of FTJ as the hardware basis of neuromorphic computational architectures. <sup>48</sup> The electrode effect on tunneling resistance in BaTiO<sub>3</sub> <sup>49</sup> and ion migration in PbZr<sub>0.52</sub>Ti<sub>0.48</sub>O<sub>3</sub> <sup>50</sup> was studied. Neuromorphic modeling and simulation were reported for BaTiO<sub>3</sub> (BTO) FTJ in the STDP circuit. <sup>51</sup> Unsupervised STDP learning was simulated for multilevel BiFeO<sub>3</sub> (BFO) FTJ. <sup>17</sup> Yamagichi *et al.* showed that the HfO<sub>2</sub> FTJ

can achieve 10<sup>3</sup> cycles by testing its reliability on the basis of time-dependent dielectric breakdown (TDDB) and stress-induced leakage current (SILC).<sup>52</sup> 1R FTJ was used for pattern recognition with off-chip learning by applying conventional voltage pulses of potentiation and depression<sup>13</sup> and spikes for spiking neural networks (SNNs).<sup>17</sup>

# 1T-1C for ferroelectric weight

The 1T-1C ferroelectric synaptic weight in ANN was suggested by Clark, Grondin, and Dey in 1989. They reported on both binary and multilevel weights, as shown in Fig. 7, and proposed incremental voltage pulses and partial switching with a short pulse width for achieving multilevel weights. The nondestructive readout (NDRO) technique has been applied to the multilevel weight by defining conductance as a weight. The NDRO mode is the same operational mode as that in the 1Tr ferroelectric weight. Obradovic *et al.* fabricated a weight cell by applying this scheme to demonstrate multilevel FeFET, in which a ferroelectric HZO capacitor is connected to the FET gate. Clark *et al.* demonstrated partial switching in a PZT capacitor by varying the pulse width and pulse voltage to demonstrate the analog programming behavior of the synapse circuit.

# Ferroelectric weight in STDP

As mentioned earlier, the STDP operation differs from that of ANN, in which relative timing between the prespikes and postspikes is converted to voltage height. Therefore, many studies have been conducted on ferroelectric synaptic weights in STDP. 11,13-17,22,5 Nishitani et al. studied the ferroelectric weight by applying STDP to a ferroelectric TFT with a structure contradictory to that of a ferroelectric transistor. 14 Boyn et al. studied the ferroelectric multilevel weight with respect to STDP, 17 and Mulaosmanovic et al. obtained STDP-like curves from ferroelectric HfO<sub>2</sub>. <sup>16</sup> Nishitani, Kaneko, and Ueda studied supervised learning by using STDP of ferroelectric TFT, and Wang et al. demonstrated ferroelectric spiking neurons for unsupervised clustering.<sup>23</sup> Furthermore, Chen et al. studied STDP and neural networks by using HZO FTJ,<sup>13</sup> and Wang et al. designed STDP for supervised learning by using 1T-1R BaTiO<sub>3</sub> FTJ. The neural network with the ferroelectric weight controlled by STDP is represented in Fig. 2.

(a) Binary weight using sense amplifier

(b) Multilevel weight using sense transistor

**FIG. 7.** 1T-1C ferroelectric weight. (a) Binary weight with destructive readout mode. (b) Multilevel weight with NDRO mode. Partially adapted from Refs. 1 and 2.

Both 1Tr with a ferroelectric capacitor and 1T-1R with a FTJ are conductance-based synaptic weights. It is important to verify whether they can be used in on-chip learning for mobile application. Figure 8 describes schematics of two- and three-terminal synapses for the STDP function. The 1T-1R weight is simple for neural networks; however, signal processing and learning cannot be simultaneously performed as reported by Nishitani *et al.*<sup>22</sup> As prespikes and postspikes are applied to the learning process, a feedback signal flow is required during learning. Such a signal can be fed to the gate of the FeFET (three-terminal) during learning but cannot be fed to a two-terminal synaptic weight. Thus, the 1Tr ferroelectric weight is indispensable when on-chip learning is required.

# Summary of ferroelectric weight

In summary, in ANN application, ferroelectrics are competitive as a synaptic weight, especially the 1T-1C type, because of their non-volatile multilevel property, as mentioned earlier. Even though they may not show perfect linearity in both potentiation and depression, their polarization level is still controllable because the curve shape of

(a) Schematics of neurons (pre-and post-) connecting via a two terminal synapse

(b) Schematics of neurons (pre-and post-) connecting via a three terminal synapse

**FIG. 8.** Schematics of neurons connecting via a two- and three- terminal synapse. (a) FTJ is used in 1T-1R synaptic weight and (b) FeFET is used in 1Tr synaptic weight. The weight value is updated in three-terminals during feedback.<sup>22</sup>

potentiation and depression is symmetric. Multilevel weights may reduce the circuit overhead, but the precise control of the polarization level is challenging. As data scattering, level resolution, and dynamic range of weight bits should be simultaneously considered, multilevels are generally limited to 16–32 levels. This implies that the dynamic range or weight bit-width of the multilevel is limited to 5 bits (32 levels) at most. The synaptic weight in ANN may require a wider bit-width. In addition, when considering level-to-level resolution, the ferroelectric weight may not be able to guarantee multilevels higher than 16 levels (4 bits) with decreasing device size.

A 1Tr-type synapse (FeFET or TFT-type FeFET) that is used in both ANN and STDP has the unique property of bistability, which is useful for excitatory and inhibitory functions. However, it is noted that a pair of n- and p-type channel materials are required for the biweight function, as demonstrated by Nishitani for a TFT-type FeFET combined with an oxide semiconductor such as ZnO. <sup>14</sup> This function is emphasized for STDP applications, where both positive and negative charge differences are defined. In addition, weighting (programming) is performed between the gate and the body of FeFET and reading is performed between the source and the drain, making the network circuit more complicated than that of a two-terminal weight. Above all, reliability, such as endurance, retention, and imprint, of ferroelectrics should be improved in advance for commercial applications.

## **FERROELECTRIC NEURON**

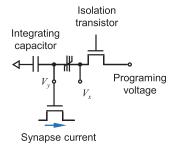

A ferroelectric neuron is defined as the CMOS neuron that contains a ferroelectric capacitor(s) or ferroelectric transistor(s). Ferroelectrics can be used in a neuron because they exhibit an integration effect in the course of partial switching. That is, the polarization state increases without discharging, because of nonvolatility, under consecutive input pulses. Moreover, a ferroelectric neuron has the same structure as that of a 1Tr weight, and it can be used with either a leaky integrator<sup>22</sup> or signal generator.<sup>15,18,21</sup> The activation function in association with a ferroelectric transistor can be achieved by devices such as unijunction transistors and oscillators.

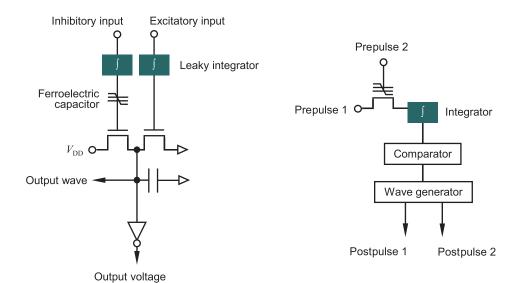

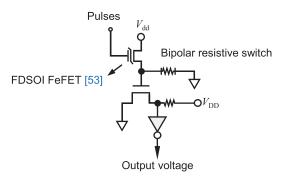

Ishiwara et al. proposed a ferroelectric neuron by utilizing ferroelectrics with pulse oscillation circuits. <sup>19</sup> Wang et al. demonstrated ferroelectric spiking neurons, as shown in Fig. 9(a),23 by connecting a ferroelectric transistor to a CMOS transistor. The ferroelectric transistor consists of a ferroelectric capacitor on the gate of the CMOS transistor (FeFET). CMOS leaky integrators are connected to the gate of the FeFET and CMOS transistor.<sup>23</sup> This combination results in an activation function. Nishitani et al. connected a ferroelectric TFT, which generates prepulses, to a CMOS integrator to generate postpulses. 15 This combination generates leaky integrateand-fire, as shown in Fig. 9(b). A recent study confirmed that a single ferroelectric transistor [fully depleted silicon-on-insulator (FDSOI) FeFET] exhibits an integrate-and-fire behavior;<sup>53</sup> the use of the integration capabilities (accumulative switching) of a nanoscale FeFET was proposed to replace the bulky integration capacitor that is normally used in neuron circuits. The activation function can be achieved by forming a circuit with a bipolar resistive switch, as shown in Fig. 9(c). It switches to the "off" state when the integrateand-fire current flows through its "on" state resulting in voltage out. A CMOS neuron consists of an integrator and an amplifier and often comprises a large capacitor to emulate the integration of the current

- (a) Ferroelectric spiking neuron. Partially adapted from Ref. 23

- (b) Ferroelectric leaky integrate and fire(LIF) neuron. Partially adapted from Ref. 15

FIG. 9. Ferroelectric neurons: (a) using the negative weight effect of the ferroelectric transistor and (b) using the STDP effect of the ferroelectric transistor. A ferroelectric capacitor with (c) integration-and-fire behavior was observed in an ultrascaled fully depleted silicon-oninsulator (FDSOI) FeFET. This effect can be used for the activation function by utilizing a current driven bipolar resistive switch that gives rise to activation voltage.

(c) FDSOI FeFET showing integrate-and-fire behavior.[53] Activation function can be realized by circuits with bipolar resistive switch.

sum from each output of neural networks. Although a ferroelectric can reduce the size of a capacitor to some extent, the scaling limitation still exists.

# **ISSUES**

Ferroelectrics such as  $PbZrO_x$  (PZT),  $SrBi_2Ta_2O_9$  (SBT),  $BaTiO_3$  (BTO), and  $BiFeO_3$  (BFO) have been investigated for the neuromorphic application. Their main issues are scalability, thickness, CMOS compatibility, and reliability including leakage current. It is relatively easier to achieve the multilevel of polarization for a large-size ferroelectric capacitor than control the polarization for a small ferroelectric capacitor because shorter pulse width and smaller incremental voltage are required for the latter.

It is desirable for the thickness of ferroelectrics in FeFET to be minimized because the thickness of the gate stack should be minimized in a vertical NAND structure. This is the reason why the ferroelectric  $HfO_2$  has attracted attention because it demonstrates ferroelectricity at the thickness of 7–10 nm and gate length of 20 nm.  $^{54}$

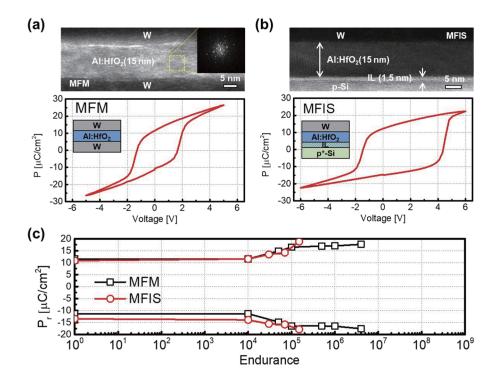

The ferroelectric transistor may be integrated in the form of metal-ferroelectric-metal-insulator-silicon (MFMIS), metal-ferroelectric-insulator-silicon (MFIS), and metal-ferroelectric-silicon (MFS). The MFS structure is desired when considering a voltage drop at the oxide gate to minimize device operational voltage. However, the direct deposition of the ferroelectric thin films on Si substrates is difficult because of the chemical reaction between Si and ferroelectric materials. <sup>18</sup> The direct deposition of HfO<sub>2</sub> on Si

also shows an unstable interface property between HfO<sub>2</sub> and Si,<sup>55</sup> although HfO<sub>2</sub> is more stable on Si than other ferroelectric materials.<sup>56,57</sup> In addition, a ferroelectric HfO<sub>2</sub> needs a large operation voltage for ferroelectric switching, thus inducing deep charge traps,<sup>58</sup> although HfO<sub>2</sub> has been used as a gate dielectric in MOS devices. Thus, the use of a semiconductor-ferroelectric-metal (SFM) structure has been attempted,<sup>10,22</sup> which is based on the model proposed by Evans.<sup>59</sup>

Inferences, such as pattern recognition, can be performed in real time when ferroelectric weight is fabricated in a neural network because vector matrix multiplication becomes possible. However, if artificial-intelligence service requires high weight bit-width, stacked weights should be integrated to reduce the neuromorphic chip size. For this purpose, the SFM integration is feasible for this purpose. Therefore, a combination of an oxide semiconductor, thin ferroelectric, and fatigue-free electrode should be intensively investigated, and a low-loss ferroelectric film with no leakage path should be selected.

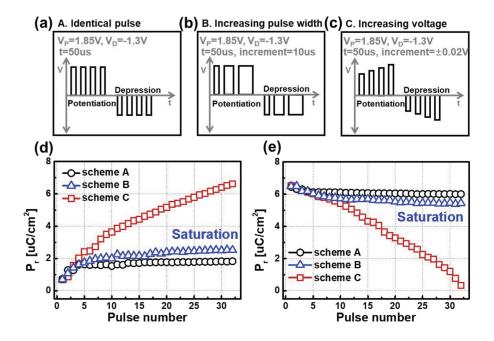

## HAFNIUM OXIDE AS AN EMERGING MATERIAL

Ferroelectric HfO<sub>2</sub> was reported in 2011 by Boscke *et al.*<sup>60</sup> and has attracted attention because it shows the ferroelectric property at a thickness less than 10 nm, which is compatible with the vertical NAND flash process. We reported the possibility of the neuromorphic synapse application using ferroelectric HZO.<sup>32</sup> The TiN/10-nm-thick HZO/TiN capacitor was evaluated under various pulse schemes, as shown in Fig. 10. It was confirmed that scheme C with incremental voltage is acceptable for achieving HZO with multilevels.

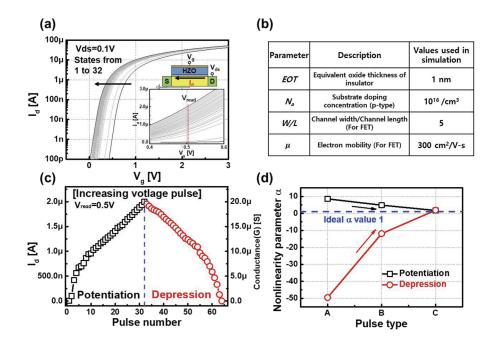

The drain current was simulated to convert the multilevel  $P_r$  into the channel current as a function of gate voltage by assuming a MFISFET. Figure 11(c) shows that the multilevel currents corresponding to each polarization state exhibit a symmetric potentiation

and depression curve. Figure 11(d) shows that nonlinearity parameter  $\alpha$  for potentiation and depression curves, in which scheme C gives a symmetric linear region.<sup>62</sup>

The ferroelectric  $HfO_2$  family transistors were investigated to confirm the presence of multilevel weights in them, as shown in Table II. Some authors focused on multilevel memory.

Ferroelectrics lose their multilevel weight effect as their size reduces as discussed earlier. When the signal control technique in Fig. 1(f) is not so practical in nanoscale ferroelectric capacitors for multilevel weights, the AND-type ferroelectric weight using the binary ferroelectric switch can be considered. But, a group of single ferroelectric cells will occupy a large area. Therefore, the stacked AND weights were proposed to reduce chip size. 42,64 Figures 12(a) and 12(b) illustrate vertically stacked AND-type and horizontally stacked ferroelectrics, respectively. In the stacked AND weight group, oxide semiconducting materials replace Si in order to reduce processing cost and avoid the reaction between Si and ferroelectric materials.

Figure 12 does not confine ferroelectric material to  $HfO_2$ . PZT combined with fatigue proof electrode SRO may be fabricated in the form of either vertical AND or horizontal AND as a matter of course. 3D integration of  $HfO_2$  has been demonstrated by IMEC for vertical processing that may be applied to a vertical NAND device.  $^{65,66}$

Ferroelectric HfO<sub>2</sub> based FeFET has several critical issues due to the interfacial layer (IL), although it is very attractive for emerging memory. The large voltage drop at the IL which has a low dielectric constant increases operation voltage for switching.<sup>67</sup> In addition, such a large voltage drop at the IL causes not only partial switching in the ferroelectric layer, not full switching, but also increases charge trapping, resulting in the reduction of memory window. Ali *et al.* reduced the operation voltage by adopting a SiON IL, which has a higher dielectric constant than SiO<sub>2</sub>.<sup>58</sup> In addition, it showed a large memory window because full switching is possible at low operation voltage and less charge trapping.<sup>58</sup> Ni *et al.* also reported that

FIG. 10. [(a)–(c)] Pulse train schemes applied to the TiN/HZO/TiN stack. (d) Potentiation and (e) depression characteristics of the polarization state of the TiN/HZO/TiN capacitor. Reproduced with permission from Oh *et al.*, IEEE Electron Device Lett. 38(6), 732–735 (2017). Copyright 2017 IEEE.

**FIG. 11.** (a) Simulation results of  $I_d$ - $V_g$  of each polarization state for scheme C and (b) the simulation parameters. (c) 32 level potentiation and depression curve at  $V_{read}$  = 0.5 V by simulation. (d) Change of nonlinearity parameter  $\alpha$  for each pulse scheme for potentiation and depression. Reproduced with permission from Oh *et al.*, IEEE Electron Device Lett. **38**(6), 732–735 (2017). Copyright 2017 IEEE.

**TABLE II.** HfO<sub>2</sub> family FET and their multiweights. P: potentiation, D: depression.

| Structure       | Materials           | Channel materials | Multilevels      | Pulse<br>scheme | $G_{\text{max}}/G_{\text{min}}$ | Operation voltage                   | Pulse width | Nonlinearity    | References |

|-----------------|---------------------|-------------------|------------------|-----------------|---------------------------------|-------------------------------------|-------------|-----------------|------------|

| FET             | Si:HfO <sub>2</sub> | Si                | ~10 to 12 levels | Incremental     | N/A                             | P: 3–5 V D: –2 to –4 V              | 1 μs        | N/A             | 16         |

| FET             | HZO                 | Si                | 32 levels        | Incremental     | 45                              | P: 2.85–4.45 V<br>D: -2.1 to -3.8 V | 75 ns       | 1.22/—1.75      | 7          |

| FinFET          | HZO                 | Si                | >32 levels       | Identical       | 4.98                            | P: 3.7 V D: -3.2 V                  | 100 μs      | 1.58/—7.57      | 9          |

| Nanowire<br>FET | HZO                 | Ge                | >256 levels      | Identical       | ~200                            | ±5 V                                | 50 ns       | 1.75/1.46       | 63         |

| TFT             | HZO                 | IGZO              | >32 levels       | Incremental     | 14.4                            | P: 2.7-4.3 V<br>D: -2 to -3.6 V     | 10 ms       | -0.8028/-0.6979 | 10         |

(a) Vertical cross-point ferroelectric AND weight stack

(b) Horizontal cross-point ferroelectric AND weight stack

FIG. 12. Stacked AND-type ferroelectric multibit weight. (a) Vertical cross-point AND stack that is compatible with vertical NAND flash processing. Partially adapted from Ref. 42. (b) Horizontal cross-point AND stack that is compatible with cross-point storage processing. Partially adapted from Ref. 59.

**TABLE III.** Strategies for endurance in HfO<sub>2</sub> based ferroelectric devices.

| Approach                        | Structure | Investigation                                                        | References |

|---------------------------------|-----------|----------------------------------------------------------------------|------------|

| Modulation of polarization axis | MFIS FET  | Trade-off between the spontaneous polarization and switching voltage | 67         |

| Subloop operation               | MFIS FET  | Reduction of the memory window                                       | 67         |

| Capacitive divider              | MFMIS FET | Complexity of the gate stack                                         | 67         |

| Channel modulation (SiGe)       | MFIS      | SiGe channel, not Si                                                 | 77         |

| Heating pulse scheme            | MFIS FET  | Complexity of the pulse scheme                                       | 78         |

charge trapping can be minimized by modulating the pulse scheme (e.g., time delay, pulse width), resulting in an increase in memory window.<sup>68</sup>

The retention and endurance of ferroelectric HfO<sub>2</sub> based FeFETs have been critical issues, although those of the MFM structure have been researched vigorously<sup>69–71</sup> and improved by NH<sub>3</sub> interface treatment.<sup>72</sup> In addition, the MFS structure is desired in order to reduce operational voltage. Therefore, retention loss and fatigue were studied for ferroelectric HfO<sub>2</sub> on Si. In the case of retention, Gong and Ma reported that ferroelectric HfO<sub>2</sub> is more suitable than conventional ferroelectric materials because of its high coercive field.<sup>73</sup> In addition, Ali *et al.* extrapolated that a 0.5-V memory window can be maintained after 10 years at 150 °C by adopting a SiON interface, which reduces the depolarization field.<sup>58</sup> In the case of endurance, IL degradation by charge trapping and trap generation induced by repetitive bipolar pulses cause endurance degradation.<sup>74–76</sup> In order to improve the endurance property, many

studies have been researched. Muller et al. suggested several strategies which can reduce voltage drop at IL during cycling.<sup>67</sup> First, they suggested the modulation of the polarization axis to reduce the effect of spontaneous polarization. Ferroelectric forms large spontaneous polarization when applied voltage, resulting in a large voltage drop at the IL. Therefore, the voltage drop in the IL can be reduced by tilting the polarization axis with respect to the surface normal of the channel. However, it has a trade-off between the spontaneous polarization effect and switching voltage because the tilted polarization axis needs large switching voltage, which leads to the increase in operation voltage. 67 Second, they suggested the use of subloop operation. The endurance property can be enhanced by using the ferroelectric subloop which needs low operation voltage, although the memory window is reduced.<sup>67</sup> In addition, they suggested that operation voltage can be reduced by adopting an IL with high permittivity. Third, they suggested the capacitive divider by modulating the area ratio of the ferroelectric layer and dielectric ILs. However,

FIG. 13. HR-TEM images and P-V curves of the (a) MFM capacitor and (b) MFIS capacitor. (c) Endurance property of the MFM capacitor and MFIS capacitor under ±6 V bipolar pulses of 10 kHz. Reproduced with permission from Oh *et al.*, IEEE Electron Device Lett. 40(7), 1092–1095 (2019). Copyright 2019 IEEE.

FIG. 14. (a) Endurance at different HPHA temperatures. (b) P-V curves and I-V curves after cycling at 100 kHz for samples without and with HPHA at 300 °C. Reproduced with permission from Oh *et al.*, IEEE Electron Device Lett. 40(7), 1092–1095 (2019). Copyright 2019 IEEE.

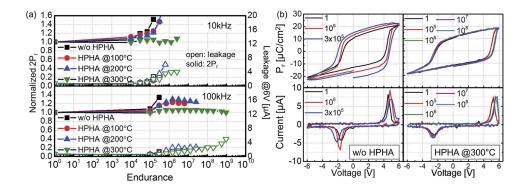

to control the area of ferroelectric and dielectric ILs separately, the MFMIS FET gate stack should be adopted. Chen et al. reported 109 cycles in the MFIS stack by adopting a SiGe channel which forms a thinner suboxide IL with better quality." Furthermore, Mulaosmanovic et al. reported recovery of the ferroelectric memory of FeFET after endurance failure by applying forward bias. 78 The local Joule heating is generated by the forward bias, which heals out the damage at the IL induced by cycling.<sup>78</sup> Therefore, they suggested optimizing the pulse scheme by adopting an alternative heating pulse. Although they are excellent strategies for endurance, they have some investigations which have to be further researched and enhanced (see Table III). In addition, the research for improving the IL by direct treatment is rarely reported, although the IL is very important for endurance in the MFIS structure. We studied the effects of high pressure hydrogen annealing (HPHA), which improves the IL quality<sup>/9</sup> on the MFIS structure.<sup>8</sup>

A 15-nm-thick poly crystalline Al doped  $HfO_2$  thin film was deposited on heavily p-doped  $Si.^{80}$  It was found that Si reacts with  $HfO_2$  to achieve the  $SiO_2$  layer, which gives rise to domain imprinting (locking or pinning) and high coercive voltage, as shown in Fig. 13(b). The increase in coercive voltage is due to the voltage drop at the  $SiO_2$  insulating layer. In addition, the resultant MFIS (W-HfO<sub>2</sub>-SiO<sub>2</sub>-p<sup>+</sup>Si) capacitor shows poor endurance as compared to that of the MFM (W-HfO<sub>2</sub>-W) capacitor, as illustrated in Fig. 13(c).

High pressure hydrogen annealing (HPHA) was performed on the MFIS capacitor at various temperatures in order to improve the capacitor properties. Figure 14 shows that endurance was improved by increasing HPHA temperature, particularly at 100 kHz. A low leakage current was maintained up to  $10^7$  cycles at  $300\,^{\circ}$ C, which led to endurance up to  $10^9$  cycles.

## **SUMMARY**

The driving force of ferroelectric materials for neuromorphic applications is their bistable memory effect, but their main drawback is the reliability of the Si process. The SFM structure, instead of MFS, may be one of the solutions to improve the reliability of ferroelectric HfO<sub>2</sub> family transistors for neuromorphic applications. SFM structure is also useful for vertical and horizontal stacked ferroelectric weights. The use of semiconducting materials such as transition metal dichalcogenide (TMD) materials and oxide semiconductors can be used for SFM structure with a potential for improving

reliability such as imprinting. However, the combination of the  $HfO_2$  family and a fatigue-free electrode needs to be discovered.

### **ACKNOWLEDGMENTS**

The authors would like to thank reviewers for their sincere advice and comments on this article. This work was supported by the National Research Foundation of Korea funded by the Korea government (MSIT), Grant No. NRF-2018R1A3B1052693.

## **REFERENCES**

<sup>1</sup>L. T. Clark, R. O. Grondin, and S. K. Dey, in *First IEEE International Conference on Artificial Neural Networks* (IEEE, 1989), pp. 47–51.

<sup>2</sup>L. T. Clark, R. O. Grondin, and S. K. Dey, in Proceedings of 11th Annual International Phoenix Conference on Computers and Communications, 1992.

<sup>3</sup>H. Ishiwara, Jpn. J. Appl. Phys. **32**, 442–446 (1993).

<sup>4</sup>E. Tokumitsu, N. Tanisake, and H. Ishiwara, Jpn. J. Appl. Phys. **33**, 5201–5206 (1994).

<sup>5</sup>Y. Kaneko, Y. Nishitani, M. Ueda, and A. Tsujimura, in *Symposium on VLSI Technology* (IEEE, 2013), pp. T238–T239.

<sup>6</sup>B. Obradovic, T. Rakshit, R. Hatcher, J. Kittl, R. Sengupta, J. G. Hong, and M. S. Rodder, IEEE J. Electron Devices Soc. **6**, 438–448 (2018).

<sup>7</sup>M. Jerry, P. Y. Chen, J. Zhang, P. Sharma, K. Ni, S. Yu, and S. Datta, in *International Electron Devices Meeting (IEDM)* (IEEE, 2017), pp. 6.2.1–6.2.4.

<sup>8</sup>M. Jerry, S. Dutta, A. Kazemi, K. Ni, J. Zhang, P. Y. Chen, P. Sharma, S. Yu, X. S. Hu, M. Niwmier, and S. Datta, J. Phys. D: Appl. Phys. **51**, 434001 (2018).

<sup>9</sup>M. Seo, M. H. Kang, S. B. Jeon, H. Bae, J. Hur, B. C. Jang, S. Yun, S. Cho, W. K. Kim, M. S. Kim, K. M. Hwang, S. Hong, S. Y. Choi, and Y. K. Choi, IEEE Electron Device Lett. **39**(9), 1445–1448 (2018).

<sup>10</sup>M. K. Kim and J. S. Lee, Nano Lett. **19**, 2044–2050 (2019).

<sup>11</sup>Z. Wang, W. Zhao, W. Kang, Y. Zhang, J. O. Klein, and C. Chappert, in International Joint Conference on Neural Networks (IEEE, 2014), pp. 29–34.

<sup>12</sup>R. Guo, Y. Zhou, L. Wu, Z. Wang, Z. Lim, X. Yan, W. Lin, H. Wang, H. Y. Yoong, S. Chen, Ariando, T. Venkatesan, J. Wang, G. M. Chow, A. Gruverman, X. Miao, Y. Zhu, and J. chen, ACS Appl. Mater. Interfaces 10, 12862–12869 (2018)

<sup>13</sup>L. Chen, T. Y. Wang, Y. W. Dai, M. Y. Cha, H. Zhu, Q. Q. Sun, S. J. Ding, P. Zhou, L. Chua, and D. W. Zhang, Nanoscale 10, 15826–15833 (2018).

<sup>14</sup>Y. Nishitani, Y. Kaneko, M. Ueda, E. Fujii, and A. Tsujimura, Jpn. J. Appl. Phys. 52, 04CE06 (2013).

<sup>15</sup>Y. Nishitani, Y. Kaneko, and M. Ueda, IEEE Trans. Neural Networks Learn. Syst. 26(12), 2999–3008 (2015).

<sup>16</sup>H. Mulaomanivic, J. Ocker, S. Müller, M. Noack, J. Müller, P. Polakowski, T. Mikolajick, and S. Slesazeck, in *Symposium on VLSI Technology* (IEEE, 2017), pp. T176–T177.

- <sup>17</sup>S. Boyn, J. Grollier, G. Lecerf, B. Xu, N. Locatelli, S. Fusil, S. Girod, C. Carrétéro, K. Garcia, S. Xavier, J. Tomas, L. Bellaiche, M. Bibes, A. Barthélémy, S. Saïghi, and V. Garcia, Nat. Commun. 8, 14736 (2017).

- <sup>18</sup> H. Ishiwara, Y. Aoyama, S. Okada, C. Shimamura, and E. Tokumitsu, Comput. Electr. Eng. 23, 431 (1997).

- <sup>19</sup>S. M. Yoon, E. Tokumitsu, and H. Ishiwara, *Extended Abstracts of the International Conference on Solid State Device and Materials* (Japan Society of Applied Physics, 1999), pp. 402–403.

- <sup>20</sup>S. M. Yoon, E. Tokumitsu, and H. Ishiwara, IEEE Trans. Electron Devices 47, 1630 (2000).

- <sup>21</sup> S. M. Yoon, E. J. Kim, Y. M. Kim, and H. Ishiwara, in *International Symposium on Nonlinear Theory and Its Applications* (IEICE, 2017), pp. 314–317.

- <sup>22</sup>Y. Nishitani, Y. Kaneko, M. Ueda, T. Morie, and E. Fujii, J. Appl. Phys. 111, 124108 (2012).

- <sup>23</sup> Z. Wang, B. Crafton, J. Gomez, R. Xu, A. Luo, Z. Krivokapic, L. Martin, S. Datta, A. Raychowdhury, and A. Khan, in *International Electron Devices Meeting (IEDM)* (IEEE, 2018), pp. 13.3.1–13.3.4.

- E. J. Kim, K. A. Kim, and S. M. Yoon, J. Phys. D: Appl. Phys. 49, 075101 (2016).

H. Wang, Q. Zhao, Z. Ni, Q. Li, H. Liu, Y. Yang, L. wang, Y. Ran, Y. Guo, W. Hu, and Y. Liu, Adv. Mater. 30, 1803961 (2018).

- <sup>26</sup> B. Tian, L. Liu, M. Yan, J. Wang, Q. Zhao, N. Zhong, P. Xiang, L. Sun, H. Peng, H. Shen, T. Lin, B. Dkhil, X. meng, J. Chu, X. Tang, and C. Duan, Adv. Electron. Mater. 5, 1800600 (2019).

- <sup>27</sup>K. M. Johnson and G. Moddel, Appl. Opt. **28**(22), 4888–4899 (1989).

- <sup>28</sup>See http://www.namlab.de/research/reconfigurable-devices/hafnium-oxide-based-ferroelectric-memory for Hafnium Oxide Based Ferroelectric Memory.

- <sup>29</sup>US 20180349761 A1, Synapse Array of Neuromorphic Device Including Synapses Having Ferroelectric Field Effect Transistors and Operation Method of the Same.

- <sup>30</sup>S. Yoon, E. Tokumitsu, and H. Ishiwara, IEEE Electron Device Lett. **20**(5), 229–231 (1999).

- <sup>31</sup>Y. Long, T. Na, P. Rastogi, K. Rao, A. I. Khan, S. Yalamanchili, and S. Mukhopadhyay, in *Proceedings of the International Conference on Computer-Aided Design* (ACM, 2018), p. 32.

- <sup>32</sup>S. Oh, T. Kim, M. Kwak, J. Song, J. Woo, S. Jeon, I. Yoo, and H. Hwang, IEEE Electron Device Lett. **38**(6), 732–735 (2017).

- <sup>33</sup>E. W. Kinder, C. Alessandri, P. Pandey, and G. Karbasian, in 75th Annual Device Research Conference (DRC), 2017.

- <sup>34</sup>Y. Ishibashi and Y. Takagi, J. Phys. Soc. Jpn. **31**(2), 506–510 (1970).

- 35 G. Zhanov, Crystal Physics (Oliver and Boyd, 1965), p. 378.

- <sup>36</sup>C. Alessandri, P. Pandey, A. Abusleme, and A. Seabaugh, IEEE Electron Device Lett. **39**(11), 1780–1783 (2018).

- <sup>37</sup>J. F. Scott, L. Kammerdiner, M. Parris, S. Taynor, V. Ottenbacher, A. Shawabkeh, and W. F. Oliver, J. Appl. Phys. 64, 787 (1988).

- <sup>38</sup> H. Mulaosmanovic, T. Mikolajick, and S. Slesazeck, ACS Appl. Mater. Interfaces 10, 23997–24002 (2018).

- <sup>39</sup>H. Mulaosmanovic, S. Slesazeck, J. Ocker, M. Pesic, S. Muller, S. Flachowsky, J. Muller, P. Polakowski, J. Paul, S. Jansen, S. Kolodinski, C. Richter, S. Piontek, T. Schenk, A. Kersch, C. Kunneth, R. ven Bentum, U. Schroder, and T. Mikolajick, in *IEEE International Electron Devices Meeting (IEDM)* (IEEE, 2015), pp. 26.8.1–26.8.3.

- <sup>40</sup> H. Mulaosmanovic, J. Ocker, S. Muller, U. Schroeder, J. Muller, P. Polakowski, S. Flachowsky, R. van Bentum, T. Mikolajick, and S. Slesazeck, ACS Appl. Mater. Interfaces 9, 3792–3798 (2017).

- <sup>41</sup>See https://www.electronicdesign.com/memory/frams-fit-wearable-electronics-glove for FRAMs Fit Wearable Electronics Like a Glove, Electronic Design.

- KR IP170017N, Vertical AND-Weight Device and Operating Method Thereof.

US 9530794B, Apparatuses Having a Ferroelectric Field-Effect Transistor Memory Array and Related Method.

- 44 E. Tsymbal and H. Kohlstedt, Science **313**(5784), 181–183 (2006).

- <sup>45</sup>L. Esaki, R. B. Laibowitz, and P. J. Stiles, IBM Tech. Discl. Bull. **13**, 2161 (1971).

- <sup>46</sup>S. Fujii, Y. Kamimuta, T. Ino, Y. Nakasaki, R. Takaishi, and M. Saitoh, in Symposium on VLSI Technology Digest of Technical Papers (IEEE, 2016), pp. 148–149.

- <sup>47</sup>B. Max, M. Hoffman, S. Slesazeck, and T. Mikolajick, in *European Soliod-State Device Research Conference (ESSDERC)* (IEEE, 2018), pp. 142–145.

- <sup>48</sup> A. Chanthbouala, V. Garcia, R. O. Cherifi, K. Bouzehouane, S. Fusil, X. Moya, S. Xavier, H. Yamada, C. Deranlot, N. Mathur, M. Bibes, A. Barthélémy, and J. Grollier, Nat. Mater. 11, 860–864 (2012).

- <sup>49</sup>R. Soni, A. Petraru, P. Meuffels, O. Vavra, M. Ziegler, S. K. Kim, D. S. Jeong, N. A. Pertsev, and H. Kohlstedt, Nat. Commun. 5, 5414 (2014).

- <sup>50</sup> C. Yoon, J. H. Lee, S. Lee, J. H. Jeon, J. T. Jang, D. H. Kim, Y. H. Kim, and B. H. Park, Nano Lett. 17, 1949–1955 (2017).

- <sup>51</sup> Z. Wang, W. Zhao, W. Kang, Y. Zhang, J. O. Klein, D. Ravelosona, and C. Chapperi, Appl. Phys. Lett. **104**, 053505 (2014).

- <sup>52</sup> M. Yamagichi, S. Fuji, Y. Kamimuta, S. Kabuyanagi, T. Ino, Y. Nakasaki, R. Takaishi, R. Ichihara, and M. Saitoh, in *IEEE International Reliability Physics Symposium (IRPS)* (IEEE, 2018).

- <sup>53</sup>H. Mulaosmanovic, E. Chicca, M. Bertele, T. Mikolajick, and S. Slesazeck, Nanoscale 10, 21755–21763 (2018).

- <sup>54</sup>S. Dunkel, M. Trentzsch, R. Richter, P. Moll, C. Fuchs, O. Gehring, M. Mager, S. Wittek, B. Muller, T. Melde, H. Mulaosmanovic, S. Slesazeck, S. Muller, J. Ocker, M. Noack, D. A. Lohr, P. Polakowski, J. Muller, T. Mikolajick, J. Hontschel, B. Rice, J. Pellerin, and S. Beyer, in *International Electron Device Meeting (IEDM)* (IEEE, 2017), p. 19.7.1.

- <sup>55</sup>N. Miyata, Materials 5, 512–527 (2012).

- <sup>56</sup>T. J. Hubbard and D. G. Schlom, J. Mater. Res. **11**, 2757 (1996).

- <sup>57</sup>B. H. Lee, L. Kang, R. Nieh, W. J. Qi, and J. C. Lee, Appl. Phys. Lett. **76**, 1926 (2000).

- <sup>58</sup>T. Ali, P. Polakowski, S. Riedel, T. Buttner, T. Kampfe, M. Rudolph, B. Patzold, K. Seidel, D. Lohr, R. Hoffmann, M. Czernohorsky, K. Kuhnel, P. Steinke, J. Calvo, K. Zimmermann, and J. Muller, IEEE Trans. Electron Devices 65(9), 3769 (2018).

- <sup>59</sup>US 5,070,385, Ferroelectric Non-volatile Variable Resistive Element.

- <sup>60</sup>T. S. Böscke, J. Müller, D. Bräuhaus, U. Schröder, and U. Böttger, Appl. Phys. Lett. 99, 102903 (2011).

- <sup>61</sup> H.-T. Lue, C.-J. Wu, and T.-Y. Tseng, IEEE Trans. Electron Devices 49(10), 1790–1796 (2002).

- <sup>62</sup>J.-W. Jang, S. Park, G. W. Burr, H. Hwang, and Y.-H. Jeong, IEEE Electron Device Lett. **36**(5), 457–459 (2015).

- $^{63} \rm W.$  Chung, M. Si, and P. D. Ye, in International Electron Device Meeting (IEDM) (IEEE, 2018), p. 15.2.1.

- <sup>64</sup>I. K. Yoo and H. Hwang, patent pending JJP0015KR00 (28 November 2018).

- <sup>65</sup>J. Van Houdt, in *IEEE International Memory Workshop (IMW)* (IEEE, 2017), pp. 1–3.

<sup>66</sup>K. Florent, S. Lavizzari, L. D. Piazza, M. Popovici, E. Vecchio, G. Potoms, and

- <sup>66</sup> K. Florent, S. Lavizzari, L. D. Piazza, M. Popovici, E. Vecchio, G. Potoms, and G. Groeseneken, in *Symposium on VLSI Technology* (IEEE, 2017), pp. T158–T159.

- <sup>67</sup>J. Muller, P. Polakowski, S. Muller, H. Mulaosmanovic, J. Ocker, T. Mikolajick, S. Slesazeck, S. Flachowsky, and M. Trentzsch, in 16th Non-Volatile Memory Technology Symposium (NVMTS), 2016.

- <sup>68</sup> K. Ni, P. Sharma, J. Zhang, M. Jerry, J. A. Smith, K. Tapily, R. Clark, S. Mahapatra, and S. Datta, IEEE Trans. Electron Devices **65**(6), 2461 (2018).

- <sup>69</sup> U. Schroeder, M. Pesic, T. Schenk, H. Mulaosmanovic, S. Slesazeck, J. Ocker, C. Richter, E. Yurchuk, K. Khullar, J. Muller, P. Polakowski, E. D. Grimley, J. M. LeBeau, S. Flachowsky, S. Jansen, S. Kolodinski, R. van Bentum, A. Kersch, C. Kunneth, and T. Mikolajick, in *European Solid-State Device Research Conference (ESSDERC)* (IEEE, 2016), pp. 364–368.

- <sup>70</sup> M. Pesic, F. P. G. Fengler, L. Larcher, A. Padovani, T. Schenk, E. D. Grimley, X. Sang, J. M. LeBeau, S. Slesazeck, U. Schroeder, and T. Mikolajick, Adv. Funct. Mater. 26(25), 4601–4612 (2016).

- <sup>71</sup> D. R. Islamov, V. A. Gritsenko, T. V. Perevalov, V. A. Pustovarov, O. M. Orlov, A. G. Chernikova, A. M. Markeev, S. Slesazeck, U. Schroeder, T. Mikolajick, and G. Y. Krasnikov, Acta Mater. 166, 47–55 (2019).

- $^{\bf 72}$  K. Y. Chen, P. H. Chen, and Y. H. Wu, in Symposium on VLSI Technology (IEEE, 2017), pp. T84–T85.

- <sup>73</sup> N. Gong and T. P. Ma, IEEE Electron Device Lett. **37**(9), 1123 (2016).

- <sup>74</sup>E. Yurchuk, S. Mueller, D. Martin, S. Slesazeck, U. Schroeder, and T. Mikolajick, in *Proceedings of the IEEE International Reliability Physics Symposium* (IEEE, 2014), pp. 2E.5.1–2E.5.5.

<sup>&</sup>lt;sup>75</sup>N. Gong and T. P. Ma, IEEE Electron Device Lett. **39**(1), 15–18

<sup>&</sup>lt;sup>76</sup>E. Yurchuk, J. Muller, S. Muller, J. Paul, M. Pesic, R. Bentum, U. Schroeder,

and T. Mikolajick, IEEE Trans. Electron Devices **63**(9), 3501–3507 (2016). <sup>77</sup> K. Y. Chen, Y. H. Huang, R. W. Kao, Y. X. Lin, and Y. H. Wu, in *Symposium on* VLSI Technology (IEEE, 2018), pp. 119-120.

<sup>&</sup>lt;sup>78</sup> H. Mulaosmanovic, E. T. Breyer, T. Mikolajick, and S. Slesazeck, <u>IEEE Electron</u> Device Lett. 40(2), 216 (2019).

<sup>&</sup>lt;sup>79</sup>H. Park, M. S. Rahman, M. Chang, B. H. Lee, R. Choi, C. D. Young, and H. Hwang, IEEE Electron Device Lett. 26(10), 725-727 (2005).

<sup>&</sup>lt;sup>80</sup>S. Oh, J. Song, I. K. Yoo, and H. Hwang, IEEE Electron Device Lett. 40(7), 1092-1095 (2019).