# SCIENTIFIC REPORTS

Received: 14 September 2016 Accepted: 15 December 2016 Published: 23 January 2017

## **OPEN** Core-shell homojunction silicon vertical nanowire tunneling fieldeffect transistors

Jun-Sik Yoon<sup>1</sup>, Kihyun Kim<sup>1</sup> & Chang-Ki Baek<sup>1,2</sup>

We propose three-terminal core-shell (CS) silicon vertical nanowire tunneling field-effect transistors (TFETs), which can be fabricated by conventional CMOS technology. CS TFETs show lower subthreshold swing (SS) and higher on-state current than conventional TFETs through their high surface-to-volume ratio, which increases carrier-tunneling region with no additional device area. The on-state current can be enhanced by increasing the nanowire height, decreasing equivalent oxide thickness (EOT) or creating a nanowire array. The off-state current is also manageable for power saving through selective epitaxial growth at the top-side nanowire region. CSTFETs with an EOT of 0.8 nm and an aspect ratio of 20 for the core nanowire region provide the largest drain current ranges with point SS values below 60 mV/dec and superior on/off current ratio under all operation voltages of 0.5, 0.7, and 1.0V. These devices are promising for low-power applications at low fabrication cost and high device density.

14-nm node fin-shaped field-effect transistors (FinFETs) have been introduced by adopting self-aligned double patterning for high integration and air-gapped interconnects to improve AC performance under operation voltage  $(V_{\rm DD})$  scaling until 0.7  $V^1$ . Ultra-thin fin width under high aspect ratio is also effective to enhance gate-to-channel controllability and obtain additional DC performance gains. However, thermionic emission transport, which all conventional metal-oxide semiconductor FETs (MOSFETs) follow, has a fundamental limit of 60 mV/dec for subthreshold swing (SS) at room temperature; satisfying high drive current while maintaining low leakage current under the  $V_{\rm DD}$  scaling is certainly difficult.

Meanwhile, tunneling FETs (TFETs) have been considered as one of the promising alternatives to attain SS below 60 mV/dec and high on/off current ratio under low  $V_{\rm DD}$  for mobile applications<sup>2-15</sup>. TFETs obey tunneling transport at the source/channel junction by adopting different types of doping between the source and the drain as p-i-n structure. However, small on-state currents  $(I_{on})$  of the TFETs are still challenging while maintaining low off-state currents ( $I_{off}$ ) concurrently. There have been several techniques to improve the  $I_{on}$  values of the TFETs in the literature. First, the electric field at the tunneling junction was increased through silicided source<sup>5</sup>, pocket between the source and channel<sup>6</sup> or micro-annealing for abrupt source/channel junction<sup>9</sup>. Second, the tunneling area was increased through adaptation of a vertical nanowire structure to increase the device density and gate-to-channel controllability<sup>4,7</sup> or modulation of the tunneling junction<sup>8</sup>. Additionally, equivalent oxide thickness (EOT) scaling or heterojunction using Ge or III-V materials was also shown to improve the DC performance by increasing gate-to-channel modulation or by decreasing tunneling barriers through low energy bandgap materials and tunneling masses, respectively<sup>13-15</sup>. However, all these lateral TFETs perpendicular to the gate electric field pose challenges to obtain precise the source/channel junction aligned to the gate region for high  $I_{on}^{16}$ . Abrupt source/channel junction and highly-doped source region are also required to boost  $I_{on}$  greatly. In addition, the reliability and variability problems of Ge17 and III-V18 materials remain unsolved.

Here we propose three-terminal silicon-based homojunction TFETs adopting a core-shell (CS) vertical nanowire structure and compare their DC characteristics to the conventional TFETs for different geometrical parameters such as the nanowire diameter ( $D_{\rm NW}$ ) and height ( $H_{\rm NW}$ ). CS TFETs are also compared to other silicon-based homojunction TFETs in terms of DC performance metrics such as Ion, Ioff, and point SS.

<sup>1</sup>Department of Creative IT Engineering and Future IT Innovation Lab, Pohang University of Science and Technology, Pohang 790-784, Korea. <sup>2</sup>Department of Electrical Engineering, Pohang University of Science and Technology, Pohang 790-784, Korea. Correspondence and requests for materials should be addressed to C.-K.B. (email: baekck@ postech.ac.kr)

.....

### Results

The point SS was extracted using two adjacent gate voltages (  $V_{\rm gs})$  and drain currents (  $I_{\rm ds})$  as

$$SS_{point} \equiv \left| \frac{I_{ds2} - I_{ds1}}{V_{gs2} - V_{gs1}} \right|$$

(1)

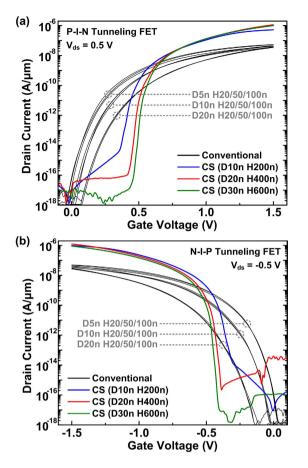

$V_{\rm gs}$  was swept from 0 to 1.5 V in steps of 0.01 V, and the drain voltage ( $V_{\rm ds}$ ) was tested at 0.5, 0.7, and 1.0 V. To compare the DC performance metrics, conventional TFETs with the  $D_{\rm NW}$  of 5, 10, 20 nm and  $H_{\rm NW}$  of 20, 50, 100 nm were considered where superior  $I_{\rm ds}$  and transconductance were attained<sup>19</sup>; the CS TFETs with  $D_{\rm NW}$  of 10, 20, 30 nm and  $H_{\rm NW}$  of 200, 400, 600 nm for the core region were simulated with the same aspect ratio of ( $H_{\rm NW}$  over  $D_{\rm NW}$ ) 20 which is acceptable for the nanowire formation<sup>20</sup>. The shell thickness ( $T_{\rm shell}$ ), the epi thickness ( $T_{\rm epi}$ ), and the EOT of the CS TFETs were fixed at 5, 20, and 1 nm, respectively, unless specified otherwise.  $I_{\rm ds}$  values were normalized to the perimeter of the nanowire ( $D_{NW} \times \pi$ ) for fair comparison between conventional and CS TFETs.

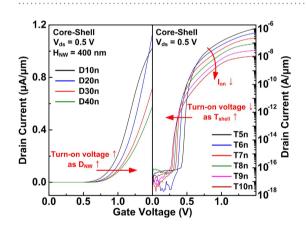

**Figure 2.** Transfer characteristics of conventional and CS TFETs with different diameters ( $D_{\text{NW}}$ ) and heights ( $H_{\text{NW}}$ ) for (**a**) n-type and (**b**) p-type operations.

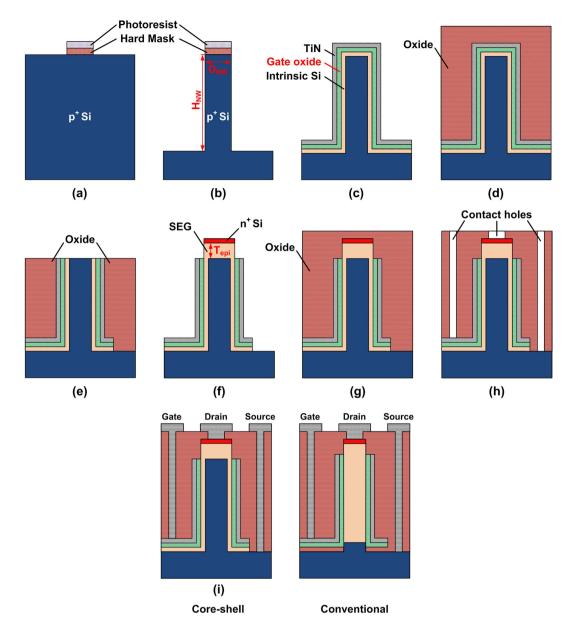

Figure 1 shows the feasibility of CS homojunction silicon vertical nanowire TFETs under conventional CMOS technology. After silicon substrate is highly doped with boron (for n-type TFETs) or with arsenic/phosphorus (for p-type TFETs), hard mask is deposited and then etched to define a vertical nanowire (Fig. 1a). A vertical nanowire with high aspect ratio is formed by inductively coupled plasma reactive ion etching, followed by advanced rinse and dry process such as critical point drying<sup>21</sup>, super-critical drying<sup>22</sup>, or Marangoni drying<sup>23</sup> to prevent the nanowire collapse (Fig. 1b). Then, low-pressure chemical vapor deposition (LPCVD) or ultra-high vacuum CVD (UHVCVD) is used to deposit undoped poly-crystalline or intrinsic silicon, respectively. Here all the CS TFETs assume to have single-crystal silicon unless specified otherwise. Atomic-layer deposition is done to form high-k gate oxide and titanium nitride metal gate regions successively (Fig. 1c). For  $SiO_2$  as a gate oxide, rapid thermal oxidation is used instead<sup>24</sup>. The core and shell regions indicate highly-doped and undoped silicon regions, respectively. After etching one-side region for the formation of the source metal contact and depositing oxide material (Fig. 1d), upper parts of the vertical nanowire regions are etched to expose the core and shell silicon regions using chemical mechanical polishing (Fig. 1e). Intrinsic undoped and highly-doped silicon are grown using selective epitaxial growth (SEG) successively for Ohmic contact formation (Fig. 1f). After depositing oxide material (Fig. 1g) and forming contact holes (Fig. 1h), finally, metal contacts are formed for the gate, drain, and source regions (Fig. 1i). Conventional vertical nanowire TFETs are also feasible under slightly different but compatible CMOS process flow<sup>4,7</sup>.

3-D numerical simulation results show superior transfer characteristics for CS TFETs (colored) compared to conventional TFETs (black) for both n-type (Fig. 2a) and p-type (Fig. 2b) operations at  $V_{\rm ds}$  of  $\pm 0.5$  V. The conventional TFETs show lower  $I_{\rm ds}$  for greater  $D_{\rm NW}$  because the electric field at the source/channel junction decreases as the gate-to-channel controllability degrades. The transfer characteristics of the conventional TFETs are independent of  $H_{\rm NW}$  in this sub-µm range<sup>19</sup> since the  $I_{\rm ds}$  is dominantly affected by tunneling at the source/channel junction, not by the series resistance at the source, channel, and drain regions unless there is direct tunneling from source to drain in the case of ultra-short  $H_{\rm NW}$  values<sup>16</sup>.

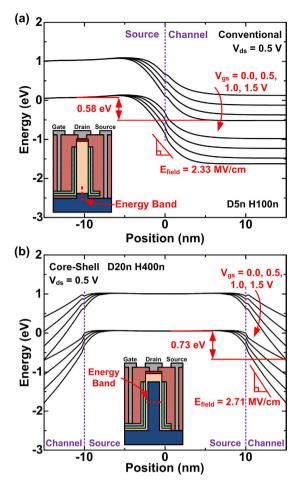

Figure 3 shows the energy band diagrams at the source/channel junctions for conventional ( $D_{\rm NW} = 5$  nm,  $H_{\rm NW} = 100$  nm) and CS ( $D_{\rm NW} = 20$  nm,  $H_{\rm NW} = 400$  nm) TFETs at  $V_{\rm gs}$  values of 0.0, 0.5, 1.0, and 1.5 V. The chosen  $D_{\rm NW}$  and  $H_{\rm NW}$  values are just one set of examples; other sets of  $D_{\rm NW}$  and  $H_{\rm NW}$  show similar band bending phenomena. The energy band diagrams are positioned at where the high band-to-band (BTB) generation rates are obtained. A sudden flexion of the energy bands near the source/channel junctions is seen because the highly-doped source regions have a smaller bandgap affected by the bandgap narrowing model. At a  $V_{\rm gs}$  of 1.5 V, the CS TFETs show higher electric field of 2.71 MV/cm than the conventional TFETs because the gate electric field

**Figure 3.** Energy band diagrams at the source/channel junctions for (**a**) conventional and (**b**) CS TFETs at different gate voltages ( $V_{gs}$ ) of 0.0, 0.5, 1.0, 1.5 V and the fixed drain voltage ( $V_{ds}$ ) of 0.5 V. Inset indicates where the energy band diagrams are from.

is exactly parallel to the electric field at the source/channel junctions<sup>25,26</sup>. In addition, more electron-hole pairs can do BTB tunneling (BTBT) for the CS TFETs because of their larger energy difference of 0.73 eV between the conduction and valence bands. In contrast, the CS TFETs have smaller maximum BTB generation rate than the conventional TFETs at a fixed  $V_{gs}$  because the tunneling carriers in the channel region are slightly apart from the silicon/insulator interface. The charge centroid by the quantum effects reduces the energy differences and thus the amount of the tunneling carriers. Because of the charge centroid, much steeper band bending at the channel region is required to initiate BTB generation for the device operation, so the CS TFETs need a greater turn-on voltage than the conventional TFETs as shown in Fig. 2. Nevertheless, the CS TFETs have a significantly wider source/channel junction for the BTBT at the nanowire sidewalls, thus increasing the  $I_{on}$  (Fig. S1).

#### Discussion

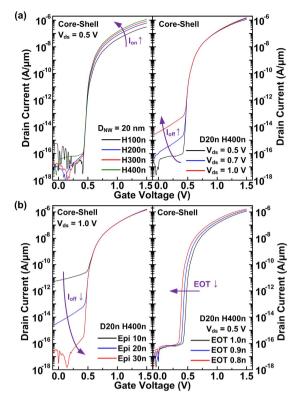

Detailed investigations of the transfer characteristics for the CS TFETs in terms of the  $H_{\rm NW}$ ,  $T_{\rm epi}$ , and EOT are shown in Fig. 4. At a fixed  $D_{\rm NW}$  of 20 nm, the CS TFETs with greater  $H_{\rm NW}$  show an increased  $I_{\rm on}$  due to the increased sidewall BTBT regions. Since the  $I_{\rm off}$  variations are affected by the tunneling currents at the top-side core regions mostly, similar off-state characteristics are obtained for different values of  $H_{\rm NW}$ . Greater  $V_{\rm ds}$  induces strong band-bending at the top-side core/epi junction and increases  $I_{\rm off}$  greatly without improving the  $I_{\rm on}$  much as shown in Fig. 4a. Although increasing  $V_{\rm ds}$  or  $V_{\rm DD}$  deviates from the main purpose to reduce the power consumption of the devices, this effect would limit the  $I_{\rm on}/I_{\rm off}$  ratio enhancement. But increasing  $T_{\rm epi}$  from 10 to 30 nm helps to reduce the  $I_{\rm off}$  critically from  $10^{-11}$  to  $10^{-16}$  A/µm with a slight  $I_{\rm on}$  degradation as shown in the left of Fig. 4b. The BTB generation rate at the top-side core/epi junction decreases as the  $T_{\rm epi}$  increases because the band bending at the top-side epi region induced by the high  $V_{\rm ds}$  is alleviated at the off-state condition (Fig. S2). Lower  $SS_{\rm point}$ , higher  $I_{\rm on}$ , and higher  $I_{\rm on}/I_{\rm off}$  ratio are obtained as the EOT decreases by adopting high-k dielectric materials. The EOT is scaled up to 0.8 nm because it is feasible and physically reliable to maintain low gate leakage current of the nanowire structure fabricated by the top-down approach<sup>18,27,28</sup>. When the gate-to-channel controllability increases for thinner EOT, more abrupt band-bending at the source/channel junction increases the electric field and thus the  $I_{\rm on}$ . Hence, the CS TFETs can achieve superior transfer characteristics when  $H_{\rm NW}$  increases and the EOT decreases under certain  $V_{\rm ds}$  and  $T_{\rm epi}$  values for low  $I_{\rm off}$ .

**Figure 4.** Transfer characteristics of the CS TFETs with (**a**) different  $H_{\text{NW}}$  and  $V_{\text{ds}}$  values and (**b**) different epi thickness ( $T_{\text{cpi}}$ ) and equivalent oxide thickness (EOT).

Figure 5. Transfer characteristics of the CS TFETs with different values of  $D_{\text{NW}}$  and shell thickness ( $T_{\text{shell}}$ ).

The transfer characteristics of the CS TFETs change with  $D_{\rm NW}$  or  $T_{\rm shell}$  (Fig. 5). Devices with  $D_{\rm NW}$  of 10 nm reduce the  $I_{\rm ds}$  at high  $V_{\rm gs}$  because of insufficient number of carriers (holes for n-type and electrons for p-type operations) at the core region for the BTBT. The decrease of  $I_{\rm on}$  for greater  $T_{\rm shell}$  and the decrease of turn-on voltage to initiate the BTB generation for smaller  $D_{\rm NW}$  or greater  $T_{\rm shell}$  can be explained in terms of simple lumped resistance-capacitance (RC) model (Fig. S3) and the energy band diagrams (Fig. S4). Assuming that  $V_{\rm ds}$  is small and/or  $T_{\rm epi}$  is thick enough to neglect the capacitive effect by the drain, there are series of resistances and capacitances between the gate and source terminals: the resistance existing at the core region ( $R_{\rm core}$ ), and capacitances at the insulator ( $C_{\rm in}$ ), depletion at the shell region ( $C_{\rm dep}$ ) and the source/channel junction ( $C_{\rm tunnel}$ ). The best performance of the CS TFETs can be attained when  $V_{\rm gs}$  is applied mostly at the  $C_{\rm tunnel}$  for higher electric field at the source/channel tunnel junction. According to the voltage divider, increasing  $C_{\rm in}$  and  $C_{\rm dep}$  and decreasing  $C_{\rm tunnel}$  and  $R_{\rm core}$  are desirable to improve the  $I_{\rm on}$ .

In accordance with the simple RC model, the variations of the transfer curves for different geometrical parameters (Figs 4 and 5) can be explained in detail. Decreasing EOT through high-k dielectric materials increases  $C_{\rm in}$  and improves DC characteristics as shown in Fig. 4b. Lower turn-on voltage for smaller EOT can also be explained by an increase in the voltage at the source/channel junction for the same  $V_{\rm gs}$  by increasing  $C_{\rm in}$ .

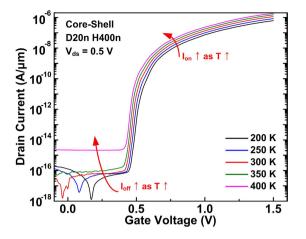

Figure 6. Transfer characteristics of the CS TFETs at the fixed  $V_{ds}$  of 0.5 V at different temperatures. The devices with different  $D_{NW}$  and  $H_{NW}$  show similar temperature dependence and thus are not shown here.

The  $R_{\text{core}}$  from the source/channel junction to the center of the core nanowire increases with  $D_{\text{NW}}$ . So, a high  $V_{\text{gs}}$  is required to apply the same electric field at the source/channel junction and initiate the BTB generation as shown in Fig. 5. But the increase of  $R_{\text{core}}$  for greater  $D_{\text{NW}}$  up to 40 nm does not affect the  $I_{\text{on}}$  much because the capacitance is dominant in this  $D_{\text{NW}}$  range. Except for the  $D_{\text{NW}}$  the way to decrease the  $R_{\text{core}}$  is to dope the core nanowire region highly.

As  $T_{\text{shell}}$  increases, the  $I_{\text{on}}$  decreases because the  $C_{\text{dep}}$  decreases and the tunneling length increases, and the tunneling current has an exponential dependence on the tunneling length (Fig. S4). Greater  $T_{\text{shell}}$  induces the BTB generation at lower  $V_{\text{gs}}$  (or turn-on voltage) even though the longer tunneling distance increases the  $SS_{\text{point}}$  at the beginning of the device operation as shown in Fig. 5. Decreasing  $T_{\text{shell}}$  is preferred to increasing the  $I_{\text{on}}$ , but too thin  $T_{\text{shell}}$  of several nanometers can increase the energy bandgap due to the quantum confinement effects<sup>29</sup>, which is disadvantageous for BTBT.

Temperature dependence of the performance of conventional and CS TFETs at  $V_{\rm ds}$  of 0.5 V is investigated in Figs S5 and 6, respectively. For both devices,  $I_{\rm off}$  increases as temperature increases to 400 K because the enhanced SRH generation increases free carriers inside the channel region<sup>30-36</sup>. A slight increase of  $I_{\rm on}$  at elevated temperature is due to the bandgap narrowing effect and thus the decreased energy barrier height at the source/channel junction. Subthreshold characteristics of both devices are independent of temperature because the source/channel junction and Si/SiO<sub>2</sub> interface are assumed to have no trap density and thus no trap-assisted tunneling (TAT) which is strongly dependent on temperature<sup>31–35</sup>. At  $V_{\rm ds}$  of 0.7 and 1.0 V for the CS TFETs with the  $T_{\rm shell}$  of 20 nm, the enhanced BTBT at the off state in the top-side intrinsic region screens the SRH generation effect and induces the same temperature dependence as the  $I_{\rm on}$  (Fig. S6).

CS TFETs having poly-Si shell regions are also investigated to understand how the crystal quality of the shell region affects the DC characteristics (Fig. S7). There are three kinds of grain boundaries (GBs) aligned at different positions within the shell region: (1) the interface between core and shell regions, (2) the middle between core and gate oxide, and (3) the middle half, which are indicated as red dotted line in Fig. S7a. All the cases degrade the DC performance by increasing  $I_{off}$  and decreasing  $I_{on}$ . Especially, the CS TFETs of the case 2 have the worst  $I_{on}/I_{off}$  ratio, about 4 orders lower than the CS TFETs with no GB. At off state, greater number of electrons and holes generated at the GB are accumulated close to the gate oxide and the core region, respectively, by the electric field at the shell region, thus contributing to  $I_{off}$  greatly. At on state, the BTBT is impeded greatly by the barrier height of the GB. For case 1, the BTBT along with the TAT at the same interface leads to the early onset of device operation. Therefore, it is required to secure the shell region made of high-quality single-crystal silicon to achieve the best DC performance.

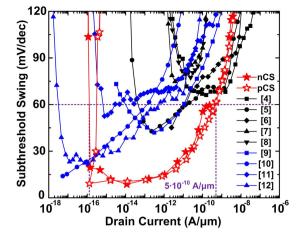

Figure 7 shows the  $SS_{point}$  with respect to the  $I_{ds}$  of the CS TFETs in this work (red), the measured<sup>4-8</sup> (black) and the simulated<sup>9-12</sup> (blue) silicon homojunction TFETs. The CS TFETs in this work have a  $D_{NW}$  of 20 nm,  $H_{NW}$  of 400 nm,  $T_{shell}$  of 5 nm,  $T_{epi}$  of 20 nm, and EOT of 0.8 nm at  $V_{ds}$  of 0.5 V. All the measured and simulated  $I_{ds}$  are normalized with respect to the device width for planar and to the perimeter for nanowire devices. The simulated data<sup>9-12</sup> show a sub-60-mV/dec of  $SS_{point}$  at lower  $I_{ds}$  ranges, which makes it difficult to substitute the conventional MOSFETs with respect to device operation speed. The measured data<sup>4-8</sup> show better subtreshold characteristics at high  $I_{ds}$  ranges, but mostly-high  $SS_{point}$  for the entire  $I_{ds}$  range is not promising for low-power applications. Among all the  $SS_{point}$  data, both n-type and p-type CS TFETs show the widest  $I_{ds}$  range from 10<sup>-16</sup> to 5·10<sup>-10</sup> A/µm under an  $SS_{point}$  of 60 mV/dec which is advantageous for higher  $I_{on}$  and  $I_{on}/I_{off}$  ratio compared to any previously-reported data<sup>4-12</sup>. In addition, both n-type and p-type CS TFETs show comparable transfer characteristics and thus are applicable to the CMOS inverter with one-to-one device ratio.

Table 1 summarizes the  $V_{\text{DD}}$ ,  $I_{\text{on}}$ , and  $I_{\text{on}}/I_{\text{off}}$  ratio for all the data in Fig. 7. The CS TFETs have the same geometrical parameters as in Fig. 7 except for the  $T_{\text{epi}}$  of 30 nm to enhance the off-state characteristics at high  $V_{\text{ds}}$  (Fig. 4b). Both n-type and p-type CS TFETs have comparable  $I_{\text{on}}$  and  $I_{\text{on}}/I_{\text{off}}$  but their lower values are shown in Table 1. After the maximum  $I_{\text{on}}/I_{\text{off}}$  ratios within the  $V_{\text{DD}}$  values are extracted from the transfer curves, the  $I_{\text{on}}$

Figure 7. Point subtreshold swing with respect to the drain currents for the best CS TFETs ( $D_{NW} = 20$  nm,  $H_{NW} = 400$  nm,  $T_{epi} = 20$  nm, EOT = 0.8 nm) at  $V_{ds}$  of 0.5 V (red), the measured data (black) and the simulated data (blue).

| References | Technology                        | EOT (nm) | $\left V_{\mathrm{DD}}\right (\mathrm{V})$ | $I_{\rm on}  ({\rm A}/\mu{ m m})$ | $I_{\rm on}/I_{\rm off}$ |

|------------|-----------------------------------|----------|--------------------------------------------|-----------------------------------|--------------------------|

| 4          | Vertical NW <sup>a</sup>          | 4.5      | 1.2                                        | $6 	imes 10^{-6}$                 | $4 \times 10^{6}$        |

| 5          | Planar                            | 0.9      | 1.0                                        | 10 <sup>-6</sup>                  | $7 \times 10^{7}$        |

| 6          | Planar                            | 3.5      | 1.1                                        | $2 	imes 10^{-6}$                 | $6 \times 10^5$          |

| 7          | Vertical NW                       | 4.5      | 0.6                                        | $6 	imes 10^{-9}$                 | $2 \times 10^3$          |

| 8          | Planar                            | 2.0      | 0.6                                        | 10 <sup>-8</sup>                  | 104                      |

| 9          | Horizontal NW                     | 1.3      | 0.5                                        | $2 	imes 10^{-8}$                 | $6 \times 10^{6}$        |

| 10         | Planar                            | 2.0      | 1.0                                        | 10 <sup>-8</sup>                  | $3 \times 10^9$          |

| 11         | Planar                            | ~0.5     | 0.3                                        | 10-9                              | $2 \times 10^3$          |

| 12         | Vertical NW<br>(NT <sup>b</sup> ) | 0.5      | 1.0                                        | $3 	imes 10^{-8}$                 | $2 \times 10^{10}$       |

| This work  | Vertical NW<br>(CS <sup>c</sup> ) | 0.8      | 0.5                                        | 10 <sup>-7</sup>                  | $4 \times 10^{10}$       |

|            |                                   |          | 0.7                                        | $3 	imes 10^{-7}$                 | $2 \times 10^{11}$       |

|            |                                   |          | 1.0                                        | $5 	imes 10^{-7}$                 | 1012                     |

Table 1. DC performance metrics of all the silicon homojunction TFETs with different EOT including measured, simulated, and this work. <sup>a</sup>NW is nanowire. <sup>b</sup>NT is nano-tube structure. <sup>c</sup>CS is core-shell structure.

.....

values at the maximum  $I_{on}/I_{off}$  ratios are obtained. All the simulated data<sup>9–12</sup> adopt the default values of A and B for the Kane's nonlocal BTBT model and thus are comparable to those of the CS TFETs. However, the comparison of DC performance between simulated and measured data is not accurate because the A and B parameters were not adjusted to the measured data beforehand. But the CS TFETs having an  $I_{on}$  of  $10^{-6}$  A/µm can achieve high  $I_{on}/I_{off}$  ratio of  $10^{10}$  at  $V_{ds}$  of 1.0 V, which has sufficiently-low  $I_{off}$  compared to the measured data<sup>4–8</sup>. Some of the simulated data<sup>10,12</sup> show  $I_{on}/I_{off}$  ratios similar to the CS TFETs, but their low  $I_{on}$  values even at high  $V_{DD}$  would decrease operation speed along with significant power consumption. Compared to the CS TFETs, the TFETs with nanotube structure<sup>12,14</sup> also show the possibility to substitute the conventional MOSFETs through high  $I_{on}$  and  $I_{on}/I_{off}$  ratio under all  $V_{DD}$  of 0.5 nm still need to be solved. Overall, the CS TFETs show comparably high  $I_{on}$  and  $I_{on}/I_{off}$  ratio under all  $V_{DD}$  of 0.5, 0.7, 1.0 V and also show great potential to increase device density through vertical nanowire structure and to adopt the nanowire array easily due to the compatibility to present a three-terminal transistor platform.

#### Conclusion

In summary, CS silicon nanowire TFETs show superior DC characteristics along with feasibility under conventional CMOS technology. They are capable of high  $I_{on}$ ,  $I_{on}/I_{off}$  ratio and sub-60-mV/dec of  $SS_{point}$  over 6 orders of  $I_{ds}$  due to their broad BTBT regions at the nanowire sidewall source/channel junctions. Greater  $T_{epi}$  through SEG process shows possibilities to reduce the  $I_{off}$  by preventing band modulation of the top-side channel region induced by the drain. The  $I_{on}$  and  $SS_{point}$  are also improved greatly when the height of the core nanowire region increases and the EOT decreases through the use of high-k gate oxide for better gate-to-channel controllability. Decreasing  $T_{shell}$  also improves the DC characteristics by decreasing tunneling length and  $C_{dep}$  at the shell region, but it remains a concern for degrading the  $I_{on}$  because a too thin  $T_{shell}$  can induce bandgap widening for the shell region due to the quantum confinement effects. Comparing all the previously-reported measured and simulated silicon homojunction TFETs, simple three-terminal CS TFETs achieve the best  $I_{on}$  and  $I_{on}/I_{off}$  ratio under ultra-low  $V_{DD}$  and also show the accessibility as a nanowire array for the drive current enhancement, thus showing potential for low-power applications.

#### Methods

Both conventional and CS nanowire TFETs were simulated using 3-D Sentaurus TCAD<sup>37</sup> with Kane's nonlocal band-to-band tunneling (BTBT) model with default parameters ( $A = 4 \times 10^{14}$  cm<sup>-3</sup>·s<sup>-1</sup>,  $B = 1.9 \times 10^{7}$  V·cm<sup>-1</sup>) for silicon as an indirect bandgap material for phonon-assisted tunneling<sup>38,39</sup>. Kane's nonlocal BTBT model is given by

$$G = A \left(\frac{F}{F_0}\right)^p \exp\left(-\frac{B}{F}\right)$$

where *G* is BTB generation rate,  $F_0 = 1$  V/cm, P = 2.5 for phonon-assisted tunneling, *A* and *B* are Kane parameters, and *F* is the electric field in the tunneling direction. Mobility was calculated using Masetti and Lombardi models for doping-dependence and degradation at the silicon/oxide interface, respectively. Bandgap narrowing model and Fermi-Dirac distribution were also included to calculate the tunneling currents correctly for the degenerate silicon regions. Shockley-Read-Hall (SRH) with doping-dependent lifetime and Auger recombination models were considered as well. In addition, a modified local-density approximation model with six-band k·p for holes and two-band k·p for electrons was used to consider the quantum confinement effects at the nanowire regions along with orientation dependency on the (001) wafer. All these mobility and bandgap-related models include the temperature-dependent factors such as carrier mobility, intrinsic carrier density, SRH generation, and energy bandgap. For the study on poly-crystalline silicon (poly-Si) shell regions, Hurkx trap-assisted tunneling (TAT) model was also included to consider trap density at the grain boundary (GB). It was assumed that there is only a single GB in the shell region, and the trap density of the GB is  $10^{13} \text{ cm}^{-2} \text{eV}^{-1}$  within the silicon energy bandgap<sup>40</sup>.

All the simulated n-type and p-type TFETs have the same doping concentrations for the core (source) regions of  $10^{20}$  cm<sup>-3</sup>, for the shell (channel) regions of  $10^{15}$  cm<sup>-3</sup>, and for the drain side of  $10^{19}$  cm<sup>-3</sup>, but they have different types of dopants: the n-type TFETs have  $p^{++}$ -i-n<sup>+</sup> structure, whereas the p-type TFETs have  $n^{++}$ -i-p<sup>+</sup> structure for the source-channel-drain regions. The drain regions have lower doping concentration than the source to lessen the ambipolar effects at the off-state condition. All the silicon regions are assumed to have uniform and abrupt doping profile. The metal gate work-functions are fixed to 4.2 eV and 5.1 eV for n-type and p-type TFETs, respectively.

#### References

- Natarajan, S. et al. A 14 nm logic technology featuring 2<sup>nd</sup>-generation FinFET transistors, air-gapped interconnects, self-aligned double patterning and a 00588 μm<sup>2</sup> SRAM cell size. Tech. Dig. Int. Electron Devices Meet. 71–73 (2014).

- 2. Appenzeller, J., Lin, Y.-M., Knoch, J. & Avouris, Ph. Band-to-band tunneling in carbon nanotube field-effect transistors. *Phys. Rev. Lett.* **93**, 196805 (2004).

- 3. Ionescu, A. M. & Riel, H. Tunnel field-effect transistors as energy-efficient electronic switches. Nat. Rev. 479, 329-337 (2011).

- Chen, Z. X. et al. Demonstration of tunneling FETs based on highly scalable vertical silicon nanowires. IEEE Electron Device Lett. 30, 754–756 (2009).

- 5. Jeon, K. *et al.* Si tunnel transistors with a novel silicided source and 46 mV/dec swing. *Tech. Dig. VLSI Symp.* 121–122 (2010).

- Chang, H.-Y., Adams, B., Chien, P.-Y., Li, J. & Woo, J. C. S. Improved subthreshold and output characteristics of source-pocket Si tunnel FET by the application of laser annealing. *IEEE Trans. Electron Devices* 60, 92–96 (2013).

- Gandhi, R., Chen, Z., Singh, N., Banerjee, K. & Lee, S. CMOS-compatible vertical-silicon-nanowire gate-all-around p-type tunneling FETs with ≤50-mV/decade subthreshold swing. *IEEE Electron Device Lett.* 32, 1504–1506 (2011).

- Huang, Q. et al. A novel Si tunnel FET with 36 mV/dec subthreshold slope based on junction depleted-modulation through striped gate configuration. Tech. Dig. Int. Electron Devices Meet. 187–190 (2012).

- Jhan, Y.-R., Wu, Y.-C. & Hung, M.-F. Performance enhancement of nanowire tunnel field-effect transistor with asymmetry-gate based on different screening length. *IEEE Electron Device Lett.* 34, 1482–1484 (2013).

- Kim, H. W. et al. Tunneling field-effect transistor with Si/SiGe material for high current drivability. Jpn. J. Appl. Phys. 53, 06JE12 (2014).

- Michielis, L. D., Lattanzio, L., Moselund, K. E., Riel, H. & Ionescu, A. M. Tunneling and occupancy probabilities: how do they affect tunnel-FET behavior? *IEEE Electron Device Lett.* 34, 726–728 (2013).

- Fahad, H. M. & Hussain, M. M. High-performance silicon nanotube tunneling FET for ultralow-power logic applications. *IEEE Trans. Electron Devices* 60, 1034–1039 (2013).

- 13. Dewey, G. *et al.* Fabrication, characterization, and physics of III-V heterojunction tunneling field effect transistors (H-TFET) for steep sub-threshold swing. *Tech. Dig. Int. Electron Devices Meet.* 785–788 (2011).

- 14. Hanna, A. N., Fahad, H. M. & Hussain, M. M. InAs/Si hetero-junction nanotube tunnel transistors. Nat. Sci. Rep. 5, 9843 (2015).

- Memisevic, E., Svensson, J., Hellenbrand, M., Lind, E. & Wernersson, L.-E. Scaling of vertical InAs-GaSb nanowire tunneling fieldeffect transistors on Si. *IEEE Electron Device Lett.* 37, 549–552 (2016).

- 16. Seabaugh, A. C. & Zhang, Q. Low-voltage tunnel transistors for beyond CMOS logic. Proc. IEEE, 98, 2095–2110 (2010).

- 17. Shifren, L. *et al.* Predictive simulation and benchmarking of Si and Ge pMOS FinFETs for future CMOS technology. *IEEE Trans. Electron Devices* **61**, 2271–2277 (2014).

- 18. Groeseneken, G. Reliability challenges for 7 nm technology. Short course, Tech. Dig. Int. Electron Devices Meet (2014).

- 19. Boucart, K. & Ionescu, A. M. Length scaling of the double gate tunnel FET with a high-k gate dielectric. *Solid-State Electron.* **51**, 1500–1507 (2007).

- 20. Seo, K. et al. Multicolored vertical silicon nanowires. Nano Lett. 11, 1851-1856 (2011).

- Passi, V. et al. Suspended silicon-on-insulator nanowires for the fabrication of quadruple gate MOSFETs. In Nanoscaled Semiconductor-on-Insulator Structures and Devices (ed. Hall, S., Nazarov, A. N., Lysenko, V. S.) 89–94 (Springer Netherlands, 2007).

- 22. Wahlbrink, T. *et al.* Supercritical drying process for high aspect-ratio HSQ nano-structures. *Microelectron. Eng.* **83**, 1124–1127 (2006).

- Tang, J. S. *et al.* Marangoni dryer integrated high performance cleaner for Cu/low k post strip clean for 45 nm technology and beyond. *Solid State Phenom.* 134, 337–340 (2007).

- 24. Hwang, H., Ting, W., Maiti, B., Kwong, D.-L. & Lee, J. Electrical characteristics of ultrathin oxynitride gate dielectric prepared by rapid thermal oxidation of Si in N<sub>2</sub>O. *Appl. Phys. Lett.* **57**, 1010–1011 (1990).

- Dey, A. W. et al. Combining axial and radial nanowire heterostructures: radial Esaki diodes and tunnel field-effect transistors. Nano Lett. 13, 5919–5924 (2013).

- Lattanzio, L., Michielis, L. D. & Ionescu, A. M. Complementary germanium electron-hole bilayer tunnel FET for sub-0.5-V operation. *IEEE Electron Device Lett.* 33, 167–169 (2012).

- 27. Monaghan, S., Greer, J. C. & Elliott, S. D. Atomic scale model interfaces between high-k hafnium silicates and silicon. *Phys. Rev. B.* **75**, 245304-1-245304-14 (2007).

- Mertens, H. et al. Gate-all-around MOSFETs based on vertically stacked horizontal Si nanowires in a replacement metal gate process on bulk Si substrates. Tech. Dig. VLSI Symp. 1–2 (2016).

- 29. Harris, C. & O'Reilly, E. P. Nature of the band gap of silicon and germanium nanowires, *Physica E.* 32, 341-345 (2006).

- Guo, P.-F. et al. Tunneling field-effect transistor: effect of strain and temperature on tunneling current. IEEE Electron Device Lett. 30, 981–983 (2009).

- Mookerjea, S., Mohata, D., Mayer, T., Narayanan, V. & Datta, S. Temperature-dependent I-V characteristics of a vertical In<sub>0.53</sub>Ga<sub>0.47</sub> As tunnel FET. *IEEE Electron Device Lett.* **31**, 564–566 (2010).

- Ganjipour, B., Wallentin, J., Borgstrom, M. T., Samuelson, L. & Thelander, C. Tunnel field-effect transistors based on InP-GaAs heterostructure nanowires. ACS Nano. 6, 3109–3113 (2012).

- 33. Riel, H. et al. InAs-Si heterojunction nanowire tunnel diodes and tunnel FETs. Tech. Dig. Int. Electron Devices Meet. 391-394 (2012).

- Rooyackers, R. et al. A new complementary hetero-junction vertical tunnel-FET integration scheme. Tech. Dig. Int. Electron Devices Meet. 92–95 (2013).

- 35. Zhu, Y., Mohata, D. K., Datta, S. & Hudait, M. K. Reliability studies on high-temperature operation of mixed As/Sb staggered gap tunnel FET material and devices. *IEEE Trans. Device Mater. Rel.* 14, 245–254 (2014).

- 36. Gandhi, R., Chen, Z., Singh, N., Banerjee, K. & Lee, S. Vertical Si-nanowire n-type tunneling FETs with low subthreshold swing (≤50-mV/decade) at room temperature. *IEEE Electron Device Lett.* **32**, 437–439 (2011).

- 37. Synopsys, Sentaurus Device User Guide (Mountain View, CA, 2016).

- Kane, E. O. Theory of tunneling. J. Appl. Phys. 32, 83–91 (1961).

Hurkx, G. A. M., Klaassen, D. B. M. & Knuvers, M. P. G. A new recombination model for device simulation including tunneling.

- IEEE Trans. Electron Devices 39, 331–338 (1992).

- 40. Kimura, M., Yoshino, T. & Harada, K. Complete extraction of trap densities in poly-Si thin-film transistors. *IEEE Trans. Electron Devices* 57, 3426–3433 (2010).

### Acknowledgements

This research was supported by the Ministry of Science, ICT and Future Planning, Korea, under the "IT Consilience Creative Program" (IITP-2016-R0346-16-1007) and also supported by IC Design Education Center.

#### **Author Contributions**

C.-K. Baek directed the experiment. J.-S. Yoon conceived the idea and performed the experiment. K. Kim provided the experimental advices and supports. All authors analyzed the data.

### **Additional Information**

Supplementary information accompanies this paper at http://www.nature.com/srep

Competing financial interests: The authors declare no competing financial interests.

How to cite this article: Yoon, J.-S. *et al.* Core-shell homojunction silicon vertical nanowire tunneling field-effect transistors. *Sci. Rep.* 7, 41142; doi: 10.1038/srep41142 (2017).

**Publisher's note:** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/

© The Author(s) 2017