## SAXS 분과

## Grazing-Incidence X-ray Diffraction을 이용한 유기반도체 구조 분석과 양극성 유기트랜지스터 어레이 응용

발표논문제목: Chemically Robust Ambipolar Organic Transistor Array Directly Patterned by Photolithography

**발표저널** : Advanced Materials, 2017, 29 (11), 1605282

저자: Eun Kwang Lee, Cheol Hee Park, Junghoon Lee, Hae Rang Lee, Changduk Yang,\* Joon Hak Oh\*

소프트 전자소자의 지속적인 관심으로 유기 반도체는 용액공정 가능성, 기계적 유연성 및 분자 설계를 통한 전기적 특성이 조절 가능하여 차세대 전자 소재로서 큰 주목 받고 있다. 최근에는 유기 전계 효과 트랜지스터 (organic field-effect transistors, OFETs)를 사용하여 센서, 논리 회로 및 발광 트랜지스터 등과 같은 많은 연구가 보고되었다. 그러나 낮은 용매 저항성으로 인한 유기 반도체의 직접적인 패턴이 어려운 점과 전자 및 정공의 불균일한 전하 수송 능력으로 상용화에 어려움이 있다.

전자 소자 제조의 상업화에서 기존의 포토리소그래피는 매우 널리 사용되는 공정이지만, 일반적으로 유기반도체 패터닝을 위해 포토리소그래피를 적용 시 유기 반도체의 심각한 성능 저하가 뒤따른다. 잉크젯 프린팅 및 쉐도우 마스크를 이용한 스프레이 코팅은 고분자 반도체를 패터닝할 때 신뢰할 만한 기술이지만 기존의 포토리소그래피에 비해 정교함과 패턴 크기에 제한을 받는다. 기존의

포토리소그래피를 사용하여 유기반도체를 패터닝하는 방법으로 유기 반도체와 포토레지스트 사이에 보호층을 도입하는 것이 보고 되었다. 한 논문에서는 패릴렌 층을 도입하여 포토리소그래피 공정 과정의 화학물질로부터 하부의 펜타센 층을 보호하여 패터닝을 하였다. 다른 연구로는, 대부분의 유기 물질은 플루오르화 된 화학 물질에 직교하는 친유성 또는 친수성을 띠어 유기 반도체에 화학적으로 손상이 없는 물질로 포토리소그래피를 사용해 패턴하였다. 또는, 소량의 광 개시제의 혼합으로 직접 광 패턴이 가능한 유기 반도체 재료가 개발되었으나 성능이 낮아 실제 적용에 문제가 있었다. 이상적으로 실제 응용에서는 포토리소그래피로 추가 공정이 없이 직접 패터닝 가능하고 화학적으로 견고하며 (여러 용매에 내 화학성을 지니는) 용액 공정이 가능한 유기 반도체 개발이 필요한 실정이다.

정공과 전자가 모두 전하 수송자로 작용하는 양극성 고분자 반도체는 유기 집적 소자 및 유기 발광 전계 효과 트랜지스터의 저렴한 제조를 위해 이상적인 후보이다. 양극성 고분자 반도체의 상업화를 위해 균형 잡힌 정공 및 전자 전하 수송에 대한 요구가 증가하고 있다. 균형 잡힌 전하 수송을 달성하기 방법으로 정공과 전자에 대한 전하주입 장벽을 최소화하는 방법이다. 이를 성취하는 손쉬운 방법은 유기 반도체의 highly occupied molecular orbital (HOMO) 및 lowest unoccupied molecular orbital (LUMO)에 대해 적절한 일 함수를 갖는 전극을 사용하는 것이다.

최근 본 연구 그룹에서는 실록산 말단 측쇄를 갖

는 diketopyrrolopyrrole (DPP)-selenophene공중합체 (PTDPPSe-Si)를 기반으로 한 고성능 양극성 OFETs 를 보고하였다. 하이브리드 측쇄의 알킬 스페이서 길이는 양 극성 성능을 최적화하기 위해 부틸에서 핵실 단위로 체계 적으로 조절하고 스페이서가 더 짧아짐에 따라 DPP 기반 의 부틸 스페이서를 갖는 PTDPPSe-SiC4에 대해 공중합 체의 용해도가 현저히 감소되어 향상된 내 화학성을 나타 내었다.

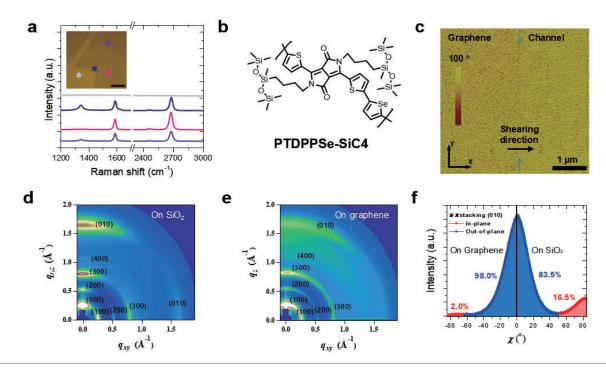

본 연구에서, 그래핀 전극이 있는 옥타데실트리클로 로실란 (OTS) 처리된SiO<sub>2</sub> / n<sup>++</sup> Si 웨이퍼 기판 위에 [그 림 1(b)]에 나타난 분자구조의 PTDPPSe-SiC4를 용액 전 단법을 통해 박막을 형성하여 연구를 진행하였다. [그림 1(a)]의 삽입된 광학 이미지는 포토리소그래피를 통해 Si 웨이퍼상의 패턴화된 그래핀 전극을 명확하게 보여주고, 라만 분광법을 통해 그래핀 전극이 잘 에칭되었음을 알 수 있다 [그림 1(a)]. 그래핀 전극과 Si웨이퍼 기판 상에 용액전단법으로 형성된 PTDPPS-SiC4 막의 표면 형태를 Atomic force microscopy (AFM) 을 이용하여 분석 하였 다 [그림 1(c)]. SiO2 표면에서는 PTDPPSe-SiC4 필름이 용액전단 공정 중에 가해진 전단 응력에 의해 고분자 사 슬의 정렬되는 것을 관찰하였고, 이와 대조적으로 그래핀 전극 위에서의 표면 형태는 무작위로 배향된 고분자 사슬 을 관찰할 수 있었다. 이것은 그래핀 특유의 2차원 벌집 모양 구조와 고분자 반도체 사이의 강한  $\pi$   $-\pi$  상호 작용 에 기인한 것으로 해석된다.

PTDPPSe-SiC4박막의 정밀한 분자 배향 및 결정도 측정을 위해 2D grazing incidence X-ray diffraction (GIXD) 분석을 수행하였다. [그림 1(d)]와 [그림 1(e)]는 각각 SiO2와 그래핀 위의 PTDPPSe-SiC4의 2D GIXD 프 로파일을 나타낸다. SiO2와 graphene상의 PTDPPSe-SiC4 박막은 out-of-plane 방향을 따라 4차까지 high order (h00) 피크를 보였다. Si의 coherence length (Lc)는 out-

그림 1. (a) 광학 이미지 (삽화)의 포인트에 따른 그래핀 전극의 라만 스펙트럼. (b) PTDPPSe-SiC4의 화학 구조. (c) PTDPPSe-SiC4의 그래 핀 및 Si 웨이퍼 위의 AFM 이미지. (d) 실리콘과 (e) 그래핀 위에서의 PTDPPSe-SiC4 2D GIXD 결과. (f)  $\pi-\pi$  stacking에 대한 (010) polar figure analysis

of-plane 방향에서 약 133Å 이었지만, 그래핀에서는 inplane 방향을 따라 약 240Å이었다. In-plane및 out-ofplane방향에서  $q = \sim 1.7 \text{Å}^{-1}$ 에서 관찰된 (010) 피크는 π-π stacking에 해당하며, SiO<sub>2</sub>상의 PTDPPSe-SiC4 박 막에서 3차원 전하 전도 채널이 형성됨을 나타냈다 [그 림1(d)]. 한편, 그래핀 전극은 out-of-plane 방향에서 만 강한  $\pi - \pi$  stacking피크  $(q_z = 1.687 \text{Å})$ 를 보였다 [그 림 1(e)]. SiO<sub>2</sub>와 그래핀 위에 제조된 고분자 필름의  $\pi$ - $\pi$ stacking을 정량적으로 비교하기 위해 (010) 회절에 대한 polar figure analysis를 수행하였다 [그림 1(f)]. SiO<sub>2</sub>상 의 PTDPPSe-SiC4는 edge-on 부분이 16.5 %이고 faceon 부분이 83.5 % 인  $\pi$  시스템에서bimodal 분포를 특징 으로 하는 반면, 그래핀 위에서는 face-on 부분이 98 %. edge-on 부분이 2 %로 보여졌다. 이를 통해 그래핀 전극 과 PTDPPSe-SiC4 간의 강한 상호 작용이 있다는 것을 확인하였다.

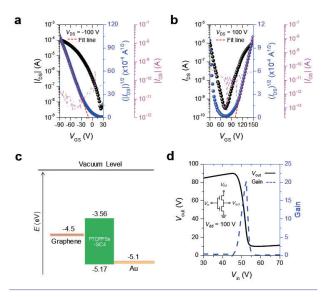

만들어진 PTDPPSe-SiC4트랜지스터의 전기적 특성은 질소 분위기에서 측정하였고, 양극성 트랜지스터는 포화 영역에서 작동하였다. [그림 2(a)]와 [그림2(b)]는 각각 그래핀 전극이 있는 PTDPPSe-SiC4 트랜지스터의 p-채널 및 n-채널 transfer curve이며, 그래핀 전극을 사용하여

그림 2. 그래핀 전극을 사용한 PTDPPSe—SiC4 FET의 (a) p—형 및 (b) n—형 transfer curve (c) 그래핀과 금의 일함수 및 PTDPPSe—SiC4 의 HOMO, LUMO 레벨을 나타내는 에너지 준위 그래프. (d) PTDPPSe—SiC4 와 그래핀 기반의 인터버 특성 그래프

양극성 특성을 보여준다. 최대 정공 및 전자 이동도는 각 각 1.43 및 0.37 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>으로 비정질 실리콘의 이동도와 비슷한 성능을 보였다. 스핀코팅, 드롭캐스트 및 용액전단 방법을 사용하여 PTDPPSe-SiC4 트랜지스터를 만들었을 시 정공 및 전자 이동도를 [표 1]과 같이 정리하였다.

표 1. 그래핀 전극과 금 전극 사용한 PTDPPSe-SiC4필름 형성 방법 (스핀코팅, 드롭캐스팅, 용액전단)에 따른 PTDPPSe-SiC4 FET전기적 성능 측정 결과

|                        | Film<br>Condition    | $[\operatorname{cm}^{2}\operatorname{V}^{1}\operatorname{s}^{-1}]$ | $[\operatorname{cm}^{2}\operatorname{V}^{-1}\operatorname{s}^{-1}]$ | $I_{\rm on}/I_{\rm off,h}$ | $[\operatorname{cm}^{2} \operatorname{V}^{1} \operatorname{s}^{-1}]$ | $[\operatorname{cm}^{2}\operatorname{V}^{-1}\operatorname{s}^{-1}]$ | $I_{\rm on}/I_{\rm off,e}$ |

|------------------------|----------------------|--------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------|

| Graphene<br>electrodes | Spin-coated          | 0.56 (±0.22)                                                       | 0.86                                                                | > 104                      | 0.06 (±0.05)                                                         | 0.11                                                                | > 10 <sup>3</sup>          |

|                        | Drop-casted          | 0.79 (±0.27)                                                       | 1.17                                                                | > 104                      | 0.09 (±0.08)                                                         | 0.22                                                                | > 10 <sup>3</sup>          |

|                        | Solution-<br>sheared | 1.00 (±0.26)                                                       | 1.43                                                                | > 10 <sup>5</sup>          | 0.20 (±0.10)                                                         | 0.37                                                                | > 10 <sup>2</sup>          |

| Gold<br>electrodes     | Spin-coated          | 0.29 (±0.03)                                                       | 0.33                                                                | > 10 <sup>5</sup>          | 0.004<br>(±0.002)                                                    | 0.007                                                               | > 10 <sup>3</sup>          |

|                        | Drop-casted          | 0.31 (±0.09)                                                       | 0.43                                                                | > 104                      | 0.004<br>(±0.002)                                                    | 0.009                                                               | > 10 <sup>2</sup>          |

|                        | Solution-<br>sheared | 0.33 (±0.08)                                                       | 0.54                                                                | > 10 <sup>5</sup>          | 0.004<br>(±0.002)                                                    | 0.009                                                               | > 10 <sup>2</sup>          |

그래핀 전극과 Cr/Au 전극을 사용하였을 때 PTDPPSe-SiC4트랜지스터의 전기적 성능을 비교하였다. Cr/Au전극을 사용할 때 전하이동도는 그래핀 전극을 사 용할 때보다 이동도가 낮았으며, Cr/Au전극을 사용한 소 자의 최대 정공 이동도는 스핀 코팅, 드롭 캐스팅 및 용 액 전단의 경우 각각 0.33, 0.43 및 0.54 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>이었 다. 스핀 코팅 기반 소자는 7 × 10<sup>-3</sup> cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>의 최대 전 자 이동도를 보인 반면. 드롭 캐스트 및 용액 전단 기반 소자는 9 × 10<sup>-3</sup> cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>의 최대 전자 이동도를 보였 다. Cr/Au전극을 가진 소자의 전자 이동도는 그래핀 전 극 소자의 ~ 5 %임을 알 수 있었다. PTDPPSe-SiC4의 HOMO 및 LUMO는 각각 -5.17 및 -3.56 eV이며, 그래핀 과 금의 일 함수는 각각 4.5와 5.1 eV이다. 따라서 금 대 신에 그래핀 전극을 사용하였을 때 전자 수송에 관하여 더 낮은 에너지 장벽을 얻을 수 있다 [그림 2(c)]. n-형 소자 구동에서 낮은 에너지 장벽은 그래핀 전극이 사용될 때 전자 수송이 유리하다는 것을 확인하였다. 반대로 금 전극에 비해 정공 수송에 대한 더 높은 에너지 장벽이 형 성되고 이는 정공 이동도에 부정적인 영향을 미치는 경향 이 있으나, [표 1]에서 볼 수 있듯이 그래핀 전극에 대한 정공 이동도와 전자 이동도가 모두 향상되었다. 이 결과 는 고분자 박막의 형태학적 요인이 에너지 준위적 요인보 다 전기적 성능에 더 큰 영향을 미쳤음을 나타낸다.

그래핀 전극을 이용한 PTDPPSe-SiC4기반 인버터 특 성은 gain이 20.3으로 보여졌으며 [그림 2(d)], 금 전극의 경우 gain이 7.9로 2배 이상 차이가 나는 것을 확인하였 다. 이러한 그래핀 전극 기반의 소자의 높은 gain은 더 균 형 잡히고 높은 전하 이동도로부터 기인됨을 알 수 있다.

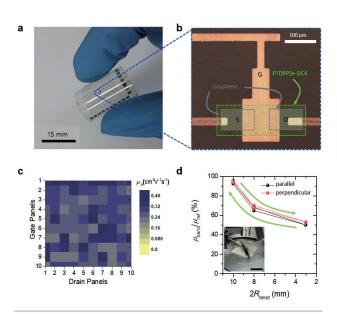

[그림 3(a)]의 삽화는 투명 폴리이미드 (PI) 위에 그래 핀 전극과 PTDPPSe-SiC4 고분자 반도체를 사용하는 개 략적인 소자 구조를 나타낸다. 패턴화 된 그래핀 전극은 SU-8 유전체/게이트 전극/투명 PI 기판 위에 준비하였 다. PTDPPSe-SiC4 반도체 층은 용액 전단을 사용하여 형성하였고, 형성된 PTDPPSe-SiC4 반도체 층은 포토레 지스트 (photoresist, PR) 코팅, 현상, 에칭 및 스트리핑 을 포함하는 일반적인 포토리소그래피 공정을 통해 패턴 화하였다. PTDPPSe-SiC4 막은 하이브리드 실록산 측쇄 그룹에 의해 유도된 높은 불용성으로 인하여 가혹한 포토 리소그래피 공정을 견딜 정도로 화학적으로 내성이 있으 며 포토리소그래피 중에 직접 패터닝 될 수 있다.

[그림 3(a)]는 투명한 PI 상의 10 × 10 FET 어레이 사 진이다. 금 게이트 전극이 없는 완전히 만들어진 어레이 구조의 투과율은 550 nm의 파장에서 91 %이다. 10 × 10 FET 어레이의 단일 트랜지스터의 광학 이미지는 [그림 3(b)]에 나타나 있다. PTDPPSe-SiC4 필름은 그래핀 전 극과 SU-8 유전체 층에 잘 정의된 패턴 구조를 보여주 고 있다. 10 × 10 FET 어레이의 평균 정공 및 전자 이동 도는 질소 분위기에서 각각 0.37 (± 0.02) 및 0.05 (± 0.02) cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>이다. PI 박막의 FET의 평균 정공 및 전 자 이동도는 Si 웨이퍼의 FET보다 약간 낮지만, PI 기판 위에 포토리소그래피 공정 후에도 PTDPPSe-SiC4 FET

그림 3. (a) 포토리소그래피를 이용해 만들어진 유연한 10×10 PTDPPSe-SiC4 FET 어레이 사진. (b) 그림 (a)에 있는 단위 소자의 광학 이미지. (c) 10×10 PTDPPSe-SiC4 FET 어레이의 정공 이동도 맵핑. (d) 유연한 10×10 PTDPPSe-SiC4 FET 어레이의 곡률 반경에 따른 이동도 변화

의 양극성이 잘 유지됨을 알 수 있었다. 실리콘 웨이퍼기반 FET과 비교하여 플라스틱 기판 위의 상대적으로 낮은 이동도는 주로 유전체와 폴리머 반도체 사이의 상이한 계면 조건 때문이다. Si 웨이퍼 상의 OTS를 처리함으로써 전하 트랩 사이트를 효율적으로 제거 할 수 있으나, SU-8 유전체 재료는 전하 채널 계면에 트랩 사이트로 작용하는 산소 원자가 포함된 관능 그룹들, 예를 들어 에테르 및 에폭시 그룹을 포함하기 때문이다. 또한 OTS 처리Si 웨이퍼에 비해 PI 필름의 표면 거칠기가 상대적으로 높아 전기 성능에 악영향을 줄 수 있다.

공기 중 조건에서  $10 \times 10$  FET 어레이의 정공 이동 도는 [그림 3(c)]와 같이 측정 되었다. 공기 중 조건에서PTDPPSe-SiC4의 n-형 거동은 산소와 물 분자와 같은 전자 트랩 때문에 공기 중 조건에서는 관찰 할 수 없었다. 용액 전단 방법을 사용하여 준비된 100 개의PTDPPSe-SiC4 FET은 최대 0.35 cm²V-1s-1, 평균 0.17 ( $\pm 0.05$ ) cm²V-1s-1의 정공 이동도를 얻을 수 있었다. 공기 중 조건에 노출된 후 진공 또는 질소 상태에서 다시 측정 할 때 소자는 양극성 특성을 회복했다.

투명한 PI 기판 상에 제조된 PTDPPSe-SiC4 FET를 이용해 유연성 테스트를 실시하였다. [그림 3(d)]는 전단 방향에 대해 평행 및 수직 방향으로 3 에서 10 mm의 곡률 반경에 따라 정공 이동도 변화를 나타낸다. PTDPPSe-SiC4 FET는 인장 변형률이1.01 %에서 3.23 %까지 변화시켜 이동도를 측정한 결과, 굽힘 반경 10, 8, 3mm에서의 정공 이동도는 초기 값의 95.5, 68.2, 50.0 %로 각각 감소하였다. PTDPPSe-SiC4 FET이 다시 평평하게 되었을 때 이동도는 초기 값으로 회복되었다. 이러한 가역적 이동도 변화는 전자소자구성 요소들 (즉, PTDPPSe-SiC4, SU-8 유전체 층)의 유연한 특성에 기인 할 수 있다.

실록산 그룹이 포함된 PTDPPSe-SiC4 필름의 화학적 내성을 측정하고자 4 가지 용매 (즉, 탈염 증류수, 에틸 알콜, 아세톤 및 클로로벤젠)를 사용하였다. 코팅된 기판 을 24 시간 동안 각 4 개의 유기 용매로 채워진 병에 넣은 후 [그림 4(a)] 용액의 UV-vis 스펙트럼을 측정하였다. 대조 필름으로서 Poly(3-hexylthiophene) (P3HT)를 동일한 환경에 측정하였다. P3HT필름의 경우 클로로벤젠의색은 노란색으로 변하고, PTDPPSe-SiC4 필름의 경우 클로로벤젠의 색은 변하지 않았다. PTDPPS-SiC4 필름이더 강한 용매 저항성을 나타내었다 [그림 4(b)].

4 가지 용매에 담그기 전 후로 PTDPPSe-SiC4 FET 소자의 정공과 전자 이동도 변화를 [그림 4(c)]와 [그림 4(d)]에 나타내었다. 제작된 소자를 24 시간 동안 4 가지 용매에 담그고, 질소 가스의 흐름 하에서 건조 후, 질소 분위

그림 4. (a) 소자의 유기용매 내성 측정을 나타내는 실험 모식도. (b) P3HT와 PTDPPSe-SiC4 를 클로로벤젠에 24시간 담근 전 후 결과 사진. 만들어진 PTDPPSe-SiC4 FET을 물, 에탄올, 아세톤, 클로로벤젠에 24시간 담근 후 (c) 정공 및 (d) 전자 이동도 변화. PTDPPSe-SiC4 FET 을 이용한 (e) 아세톤 센싱 실험 모식도 및 (f) 아세톤 증기의 노출에 따른 전류 변화

기 하에서 220 ℃에서 30 분 동안 어닐링시켰다. 소자의 정공 이동도와 전자 이동도는 처음에 비해 약간 감소되 었지만 모든 소자는 용매 노출 후에도 잘 작동함을 알 수 있었다. 이러한 결과는 중합체의 높은 불용성으로 인해 PTDPPSe-SiC4의 우수한 화학적 견고성을 입증한다.

화학 센서 용 플랫폼으로서 가능성을 간단히 살펴보 기 위해, PTDPPS-SiC4 FET위에 ON/OFF 스위칭[그림 4(e)]이 가능한 아세톤 증기를 4 SLM 속도로 노출시켰다. 아세톤 증기 감지 응답은 [그림 4(f)]에 나와 있다. 아세톤 증기에 노출되면 드레인 전류가 감소하는 음 감지 거동을 나타내었다. 극성 물질의 증기가 유기반도체 층에 노출 되면 유기 반도체 층의 입자 경계에서 쌍극자에 의해 유 도된 전하 트래핑 때문에 홀 전류가 감소한다. 아세톤은 극성 및 전자 전자주개 물질이어서 예상대로 홀 전류에 서 음의 감지 신호를 보여 주었다. PTDPPS-SiC4 FET기 반의 아세톤 센서는 아세톤 가스 OFF 영역에서 안정적인 작동을 보였으며 20 사이클에 걸쳐 아세톤 가스 ON 영 역에서 약간의 감지 편차를 보였다. ON 영역에서  $I_D/I_{Base}$ 의 평균값은  $\sim 0.75$ 이었다. 소자의 감도 (S =  $I_{acetone-off}/$  $I_{\text{acetone-on}}$ , 아세톤 가스 OFF와 ON 조건의 드레인 - 소스 전류의 비율로 정의 됨)는 1.3이었다. 아세톤 가스 흐름에 노출된 후 소스 - 드레인 전류는 즉시 감소하여 0.88 초 의 응답 시간을 보였다. 아세톤 가스 흐름을 차단하면 전 류가 2.63 초 (복구 시간)의 포화 전류 수준까지 회복되었 다. 회복된 시간은 반응 시간보다 길었으며, 이는 흡착된 아세톤 분자가 자연스럽게 소자로부터 탈착되기까지 시 간이 필요하기 때문이다.

본 연구는 화학적으로 견고한 유기 반도체 PTDPPSe-SiC4와 그래핀 전극을 사용하여 기존의 포토리소그래 피를 통해 균형 잡힌 정공 및 전자 이동도를 갖춘 양 극성OFET 어레이를 제작하는 것에 대해 보고하였다. PTDPPSe-SiC4의 높은 불용성으로 유기 반도체는 통상 적 인 포토리소그래피에 의해 직접 패터닝 될 수 있었 다. 그래핀과 PTDPPSe-SiC4 사이의 낮은 장벽과 강한 분자간 상호 작용으로 인해 그래핀 전극의 접촉 저항은 Cr/Au 전극의 접촉 저항보다 훨씬 낮음을 확인하였다. PTDPPSe-SiC4 FETs는 다양한 용매에 담근 후에도 정상 적으로 작동하여 PTDPPSe-SiC4의 화학적 견고성을 입 증하였다. 본 연구의 결과는 양극성 OFET에서 균형 잡힌 전하 수송을 향상시키는 중요한 단계이며, 기존의 마이 크로 전자 기반 구조에서 고분자 반도체의 적용 가능성 을 입증하여 플라스틱 전자 제품의 실현을 이끌 것으로 기대 된다.

## 참고문헌

[1] J. Lee, A. R. Han, H. Yu, T. J. Shin, C. Yang, J. H. Oh, J. Am. Chem. Soc. 2013, 135, 9540.

[2] J. Lee, A. R. Han, J. Kim, Y. Kim, J. H. Oh, C. Yang, J. Am. Chem. Soc. 2012, 134, 20713.

## 저 자 약 력

이은광 박사는 2017년 UNIST 에너지 및 화학공학과에서 박사학위를 취득하였고, 현재 POSTECH 화학공학과에서 박사 후 연구원으로 재직 중이다.

eklee@postech.ac.kr

오준학 교수는 2004년 서울대학교 화학생물 공학부에서 박사학위를 취득하였고, 삼성전자 책임연구원 (2004~2006), Stanford Univers ity 박사 후 연구원 (2006~2010), UNIST 에 너지 및 화학공학부 조교수 (2010~2013) 를 거쳐, 현재 POSTECH 화학공학과에서 부교 수로 재직 중이다.

joonhoh@postech.ac.kr